과도금된 글래스 표면, CMP로 평탄화

CMP 장비⋅소재 수요 촉발 전망

반도체 업계가 차세대 패키지 솔루션으로 낙점한 글래스 코어 기판 제조에 CMP(화학기계적연마) 공정 도입이 검토되고 있다. CMP는 반도체 팹 공정에서 웨이퍼 표면을 평탄화 하기 위해 고안한 기술로 그동안 후공정단에서 사용된 바는 없다.

반도체 업계가 이르면 2025년 이후부터 글래스 코어 기판을 양산할 예정이어서 CMP 장비⋅소재 수요도 늘어날 것으로 예상된다.

과도금된 글래스 표면, CMP로 평탄화

반도체 업계가 패키지 기판 코어 소재를 플라스틱의 일종인 ‘FR4’에서 글래스로 교체하려는 이유 중에는 글래스 위에 더 많은 수의 비아홀을 배치할 수 있다는 점이 크게 작용한다. 비아홀의 밀도가 높다는 뜻이다. 코어를 관통하는 비아홀이 많을수록 반도체 칩으로부터 나온 데이터를 더 빠르게 입출력할 수 있다.

다만 같은 면적에 더 많은 비아홀을 배치하자면 개별 비아홀 직경은 작아져야 하고, 결과적으로 비아홀의 종횡비(높이/직경)는 높아진다.

여기서 기존 패키지 기판과 글래스 코어 기판의 도금 방식에 차이가 생긴다. 종전 FR4 기반 패키지 기판의 코어는 비아홀 내벽을 도금하는 방식이다. 비아홀 내부를 가득 채우지는 않는다.

이에 비해 글래스 코어 기판은 비아홀 직경이 상대적으로 좁기에 홀 내벽만 도금할 수는 없다. 내부 공간을 가득 채워 전도성을 부여한다.

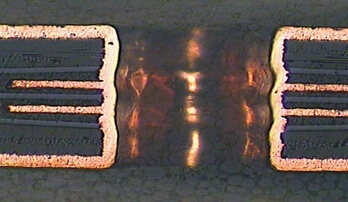

다만 홀 내부 공간을 가득 채우기 위해서는 도금 시간이 길어져야 하고, 이 과정에서 홀 상부에 필요 이상의 도금이 이뤄진다. 홀 윗부분이 반구 형태로 볼록하게 튀어 나오는 것이다.

패키지 기판 업계가 글래스 코어 기판 제조에 CMP 공정 도입을 검토하는 건 이 과도금된 구리를 깎아내기 위해서다. 홀 위로 구리 도금이 높게 솟아 있으면 이는 향후 절연층인 ABF(아지노모토빌드업필름) 빌드업 과정에서 수율에 나쁜 영향을 줄 수 있다.

특히 글래스 코어 기판은 AI(인공지능)나 HPC(고성능컴퓨팅)용 칩 패키지에 사용될 가능성이 높고, 이를 위해서는 패키지 기판의 L/S(라인앤드스페이스, 회로 선폭)도 좁혀야 한다. 현재 고성능 칩 패키지용 L/S는 12μm/12μm 혹은 9μm/12μm 정도다. 글래스 코어 기판 상 L/S는 이보다 더 축소될 가능성이 높다. 이처럼 미세한 선폭을 구현해야 하는 기판에서 수직으로 솟은 도금이 수율을 저해할 수 있다.

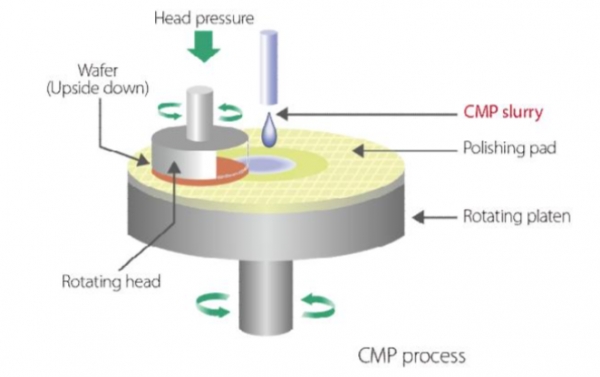

CMP는 기판 표면을 CMP 패드 위에 열과 압력을 가해 문지르는 방식으로 이뤄진다. 이 과정에서 높게 솟은 구리 도금이 깎여 나가면서 평탄화되는 원리다.

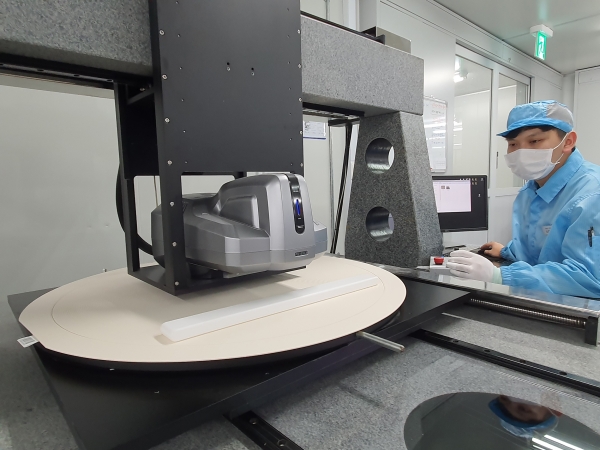

아직 검토단계이기는 하지만 CMP가 실제 글래스 코어 기판 양산에 적용된다면 CMP 장비⋅소재 수요를 촉발할 수 있다. CMP 장비는 미국 어플라이드머티어리얼즈가 절반이 넘는 점유율을 보유하고 있고, 일본 에바라, 우리나라 기업인 케이씨텍이 나머지 점유율을 양분한다. 기재의 표면을 문지르는데 쓰는 CMP 패드는 미국 듀폰이 한때 80% 이상의 점유율을 보유하고 있었으나, 최근 SKC 자회사인 SK엔펄스가 점유율을 높여가고 있다.

CMP 공정에 사용하는 CMP 슬러리는 3M⋅듀폰⋅캐봇 등 미국 회사와 JSR⋅후지필름⋅신에츠 등 일본 회사들이 조금씩 점유율을 나눠갖고 있다. 케이씨텍도 CMP 장비와 함께 슬러리를 공급한다.

다만 CMP 공정이 글래스 코어 기판 제조에 실제 양산 적용될지에 대해서는 아직 반론도 없지 않다. CMP 공정 자체가 워낙 고가의 기술이어서다. 특히나 팹 공정 대비 대비 패키지 기판 제조는 부가가치가 낮다. 고가의 팹 기술이 도입되기에는 타당성을 좀 더 검토해봐야 한다.

이에 CMP 공정 대신 저렴한 ‘브러시(Brush)’ 공정으로 평탄화 작업을 대신하려는 시도도 있는 것으로 알려졌다. 한 반도체 산업 전문가는 “브러시 공정으로는 유리 표면에 결함이 발생할 가능성이 높다”며 “이 때문에 삼성전기⋅SKC앱솔릭스 등이 브러시와 CMP 공정을 놓고 비교하고 있다”고 말했다.