씨드 두께 줄여 '사이드 로스' 감소

작업 속도 지연 및 투자비 증가는 문제

반도체 업계가 차세대 패키지 기판 기술로 개발하는 글래스 코어기판에 스퍼터 공정이 최소 두 군데 이상 적용될 전망이다. 스퍼터는 원래 반도체⋅디스플레이 전공정에서 박막증착을 위해 주로 쓰였고, 반도체 후공정에는 팬아웃 등 첨단 패키지 일부에만 제한적으로 사용돼 왔다.

스퍼터 공정이 적용되면 미세 패턴 구현에는 유리하지만 작업속도가 늦고 설비투자비가 증가한다.

ABF 씨드층 형성에도 스퍼터 검토

현재 글래스 코어기판을 생산하는 과정에서 스퍼터 공정이 도입됐거나 검토되는 곳은 ▲TGV(글래스관통전극) 기판에 전기를 통하게 하기 위한 메탈 씨드층 형성 ▲ABF(아지노모토빌드업필름) 상에서 mSAP 공정시 씨드층 형성 두 곳이다.

이 가운데 TGV 기판에 금속 씨드를 입히기 위한 스퍼터 공정, 이른바 메탈라이제이션은 이미 많은 TGV 업체들이 도입한 바 있다. 앱솔릭스의 TGV 협력사인 에프앤에스전자가 인천 송도 TGV 양산 라인에 스퍼터를 이용해 메탈라이제이션 공정을 구축했으며, TGV 전문업체 중우엠텍⋅제이앤티씨 역시 메탈라이제이션 기술로 스퍼터를 택했다.

반면 ABF 상에 씨드층을 형성하기 위해 스퍼터를 적용하는 방안은 아직 확립되지 않았다. 비교적 최근들어 반도체 업계가 글래스 코어기판을 개발하는 벤더들에게 요청하고 있는 것으로 알려졌다.

ABF는 패키지 기판에 미세회로를 구현하기 위해 사용하는 절연 소재다. ABF에 회로를 만들기 위해서는 mSAP(Modified Semi Additive Process)으로 도금 패턴을 만들어야 하는데, 그에 앞서 이뤄지는 게 씨드층 형성이다. 씨드층은 mSAP에서 전기동을 올릴 때 도금이 잘 일어나게 하기 위해 필요한 레이어다.

현재 ABF 씨드층 형성에 일반적으로 사용하는 기술은 무전해 화학동이다. 무전해 화학동은 전기를 통하지 않고 촉매를 이용해 소재(구리)를 석출시키는 방식이다. 이는 현재 양산되는 FC-BGA(플립칩-볼그리드어레이) 등 다양한 고밀도 패키지 기판 제조에 널리 적용되고 있다.

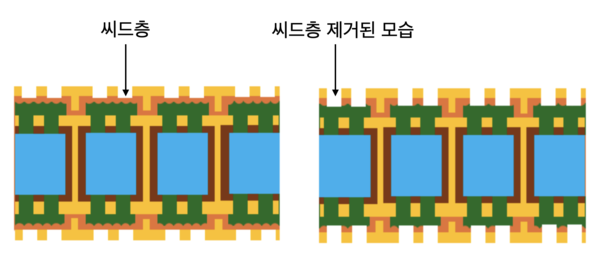

문제는 화학동 기술로 만든 ABF 씨드층은 두께를 줄이는 데 한계가 있다는 점이다. 현재 PCB(인쇄회로기판) 업계 최신 기술로 구현할 수 있는 화학동 최소 두께는 0.4μm(마이크로미터)다. 씨드층은 mSAP의 마지막 단계에서 ‘플래시 에칭(식각)'으로 제거해야 하는데, 두께가 너무 두꺼우면 플래시 에칭 과정에서 주변 회로까지 더불어 식각되는 부작용이 발생한다.

수직(씨드층) 방향은 물론 수평(회로) 방향으로 동일하게 금속이 깎여나가는 ‘등방성(Isotropic) 식각'이 일어나기 때문이다. 이를 인접 회로가 손상을 입는다는 의미에서 ‘사이드로스’라고 칭한다.

스퍼터를 이용해 ABF 씨드를 만들면 사이드로스를 최소화 할 수 있다. 스퍼터로 구현할 수 있는 씨드층의 최소 두꼐는 0.1~0.15μm에 불과하다. 플래시 에칭 속도가 동일하다면 에칭 시간을 최저 4분의 1로 줄여도 씨드층을 모두 제거할 수 있다. 플래시 에칭 과정에서 인접 회로가 같이 깎여나갈 여지를 그 만큼 줄인다.

L/S 폭 감소 탓에 일어나는 문제

사실 플래시 에칭 과정에서 발생하는 사이드로스는 이전에도 없지 않았다. 다만 패키지 기판의 L/S(라인앤드스페이스, 회로폭)가 수십μm로 두꺼울때는 사이드로스가 큰 문제가 되지 않는다. 1μm 안팎까지 회로 옆면이 깎여 나가도 기본 패턴 자체가 두껍기 때문이다. 신호전달이 잘 일어난다는 뜻이다.

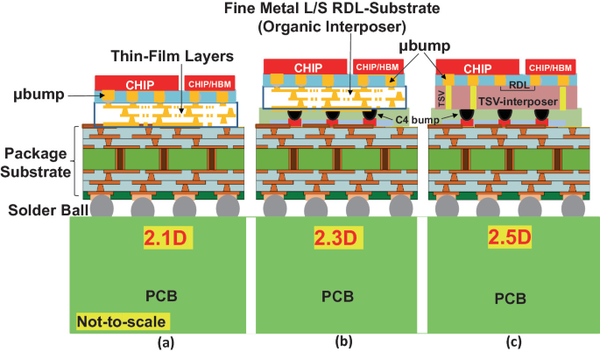

그러나 반도체 업계가 상정하는 글래스 코어기판은 기존 패키지 기판과는 쓰임이 다르다. AI(인공지능)용 HPC(고성능컴퓨팅) 중에서도 최상위 반도체 패키지에 글래스 코어기판이 사용될 가능성이 높다. 따라서 기판 위에 올라오는 L/S도 이전보다 대폭 줄어든 수μm 수준에 불과할 수 있다.

인터포저가 빠진 2.1D 패키지 컨셉트에서 GPU(그래픽처리장치)와 HBM(고대역메모리)을 연결하기 위한 L/S는 2/2μm다.

회로 두께가 평균 2μm에 불과한데 플래시 에칭 과정에서 0.4μm, 혹은 그 이상이 깎여 나간다면 신호 전달이 끊길 수도 있다. 이에 반도체 업계가 ABF 씨드층에 화학동이 아닌 스퍼터를 사용할 것을 요청하는 것이다.

한 반도체 산업 전문가는 “스퍼터를 쓰면 사이드로스 문제를 상당부분 해결할 수 있지만, 이에 따른 막대한 투자비를 감당해야 한다”며 “이 때문에 패키지 기판 업계가 도입을 꺼려하고 있다”고 말했다.