CoWoS, 엔비디아 GPU 모듈 위한 2.5D 패키지

현재는 TSMC 내부 생산능력에 의존

최근 엔비디아가 불러 일으킨 반도체 시장 훈풍은 정확하게는 ‘AI 반도체’로 불리는 서버용 GPU(그래픽처리장치) 시장에 제한적으로 불고 있다. 아직 메모리 반도체 산업 전반적으로 재고가 산적하지만 GPU 모듈을 구성하는 HBM(고대역폭메모리) 수요만큼은 견조한 게 그 증거다.

그러나 GPU 수퍼 사이클을 타고 HBM 출하가 지속적으로 늘기 위해서는 TSMC의 CoWoS(칩온웨이퍼온서브스트레이트) 병목이 시급히 풀려야 한다.

AI 반도체의 병목, CoWoS

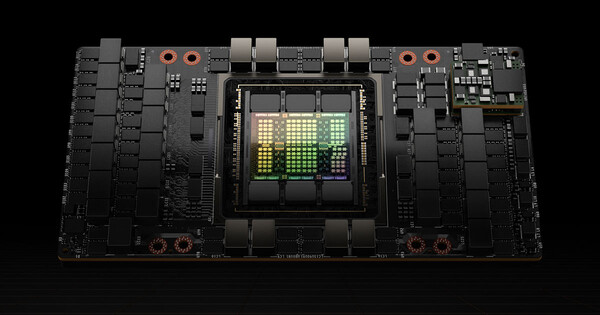

‘챗 GPT’ 등 생성형 AI 서비스를 제공하려면 다량의 GPU 자원이 필요하다. 그 총아가 엔비디아의 데이터센터용 코어 GPU 모듈인 A100⋅H100이다. 두 제품은 미국이 중국과의 반도체 전쟁 초기 중국으로의 수출을 제한한 품목이기도 하다.

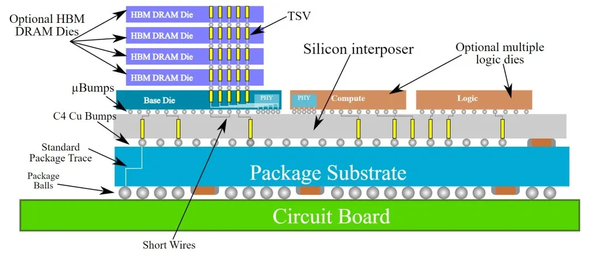

A100⋅H100이 일반 PC용 GPU와 가장 크게 다른 점은 HBM이 GPU와 2.5D 패키지 기술로 한 몸처럼 묶여 있다는 점이다. 2.5D 패키지란 인터포저가 들어간 FC-BGA(플립칩-볼그리드어레이) 기판 위에 여러가지 칩을 병렬로 한번에 묶은 제품을 뜻한다.

2.5D 패키지는 칩을 수직으로 쌓는 3D 패키지는 아니지만 3D와 마찬가지로 높은 전송속도를 구현한다. 3D 패키지 처럼 TSV(스루실리콘비아)를 위한 구멍을 여러번 뚫을 필요가 없기에 실리콘 면적 손실이 적고, 제조 수율도 높다. 엔비디아의 최신 A100 80GB 모델은 메모리 대역폭이 1초당 2TB(테라바이트)에 이른다. AI 학습⋅추론을 위해서는 GPU와 메모리 간에 데이터를 빠른 속도로 주고 받아야 하기에 메모리 대역폭이 곧 AI 성능을 결정한다.

따라서 AI 반도체의 출하량은 2.5D 패키지 기술에 의존도가 높으며, A100⋅H100은 100% TSMC의 CoWoS를 통해 생산되고 있다. CoWoS는 TSMC의 2.5D 패키지 기술의 브랜드명이다.

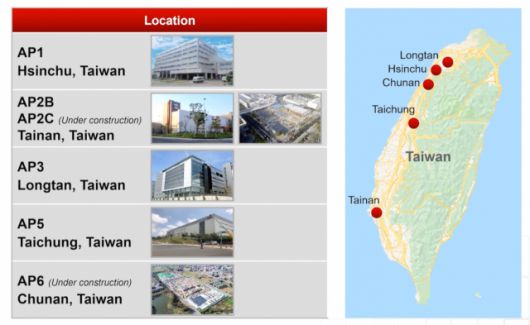

TSMC는 대만 북부 주난에 신설한 AP6 공장에서 CoWoS 공정을 제공한다. AP6는 TSMC가 CoWoS, InFo(팬아웃웨이퍼레벨패키지) 등 첨단 패키지 공정을 수행하기 위해 투자했다. 지난해 3분기 가동을 시작했으며, 아직 신규 설비들이 반입되는 중이다.

현재 TSMC의 CoWoS 패키지 생산능력은 300㎜ 웨이퍼 월 8000~9000장분 정도인 것으로 추정된다. 연간으로 10만장 안팎인 셈이다. 현지 매체 디지타임스에 따르면 엔비디아는 최근 TSMC로부터 CoWoS 생산능력 1만장 가량을 연말까지 추가 제공받기로 확약 받았다.

‘확약 받았다’는 것은 수요 대비 공급이 부족하다는 의미다.

CoWoS를 통해 생산되는 반도체 모듈은 구글 ‘TPU’, 아마존 ‘트레이니엄’, AMD ‘베가’ 등 다양하다. 다만 업계는 TSMC의 CoWoS 생산능력 대부분은 현재 엔비디아에 할당된 것으로 추정한다.

한 반도체 업계 전문가는 “A100이 생산되는 7nm(나노미터), H100의 4nm은 물론 D램 업체들의 HBM 생산능력도 어느 정도 여유가 있으나 CoWoS는 풀 가동으로도 생산량을 맞추기 힘든 상태”라고 설명했다.

발빠르게 증설 않는 TSMC

이처럼 수요가 탄탄하고 생산능력마저 부족하면 공격적인 투자에 나설 법도 한데 TSMC의 행보는 느긋하다. CoWoS 장비가 반입되고 있는 주난 AP6에 반입을 서두르는 등의 정황은 아직 보이지 않는다. AP6는 AP6A, AP6B, AP6C 등 3개 구역으로 나뉜다. 현재 장비가 반입되고 있는 공장은 AP6A 하나로, B⋅C는 여전히 건설 중이다. 대만⋅일본⋅미국⋅유럽 등 지역을 가리지 않고 첨단 파운드리 팹 투자에 속도를 높이고 있는 것과는 상반된 행보다.

이에 대해 반도체 업계는 팹 공정을 우선시하는 TSMC의 그간 행보에 비춰 설명한다. TSMC는 팹 대비 상대적으로 부가가치가 떨어지는 패키지 공정은 고객사 프로모션 차원에서 개발하지만, 이를 대규모 양산하는 건 전문 OSAT(외주패키지⋅테스트) 업계에 맡기는 원칙을 고수한다. CoWoS 공정 내에서도 더 부가가치가 낮은 부분은 외부 업체로 돌리는 방식으로 오버헤드를 떨어뜨린다.

실제 미국 앰코테크놀로지, 대만 ASE 등도 TSMC로부터 일감을 받기 위해 CoWoS 전체 공정 내지 일부 공정에 투자하고 있다. 한 반도체 후공정 업체 임원은 “TSMC는 첨단 패키지 기술을 통해 부가가치를 창출한다기 보다 자신들이 생산한 칩의 패키지 레퍼런스를 보여줄 정도만 투자한다”며 “제한된 리소스를 팹 공정에 투자하고자 하는 집중 방식”이라고 설명했다.