YMTC가 낸드플래시 업계서 첫 도입

삼성전자⋅SK하이닉스⋅마이크론도 도입 준비

1장 더 필요한 웨이퍼 비용과 공정 구축은 부담

최근 3D 낸드플래시 업계에선 ‘하이브리드 본딩’이 화두다. CIS(이미지센서) 상⋅하판을 이어 붙이는데 널리 쓰이는 기술인 하이브리드 본딩은 3D 낸드플래시 분야에서는 중국 YMTC가 처음 도입했다.

첫 양산때만 해도 크게 주목받지 못했으나 YMTC가 200단 이상 제품 개발에 성공하는 등 성과를 보이면서 선발 업체들도 관련 기술 도입을 검토하고 있다.

웨이퍼 2장 이어 붙이는 하이브리드 본딩

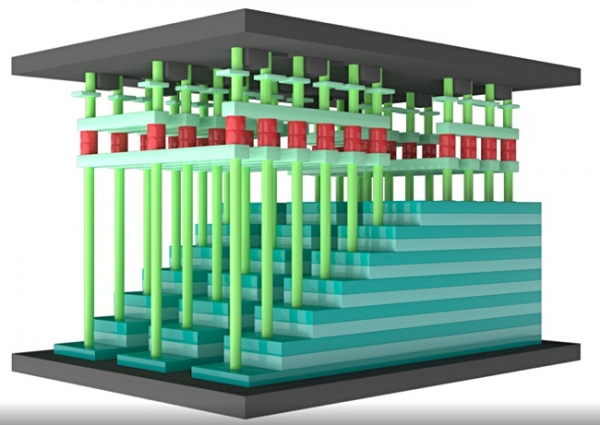

원래 3D 낸드플래시는 정보를 저장하는 셀과 각 셀을 구동하는 주변부 회로(Peri)가 한 장의 웨이퍼 위에 만들어진다. 초창기 주변부 회로가 셀 옆에 위치했다가, 최근에는 집적도 개선을 위해 셀 아래 위치하는 게 일반적이다. 마치 아파트 주차장을 지하로 넣어 지상 공간을 다른 용도로 활용하는 것과 같다. 이를 ‘페리 언더 셀(PUC)’, 혹은 ‘셀 온 페리(COP)’ 방식이라고 부른다.

하이브리드 본딩을 3D 낸드플래시 생산에 도입한다는 건 주변부 회로와 셀을 각각의 웨이퍼 위에서 생산한다는 뜻이다. 완성된 주변부 회로와 셀을 정밀하게 이어 붙여 하나의 낸드플래시로 만든다.

3D 낸드플래시 업계에서 이러한 방식을 가장 먼저 시도한 회사가 YMTC다. YMTC는 파운드리 업체 SMIC가 생산한 주변부 회로 웨이퍼와 자신들이 직접 생산한 셀 웨이퍼를 이어 붙여 3D 낸드플래시를 생산한다. 이를 자체적으로 ‘엑스태킹(Xtacking)’으로 명명한다.

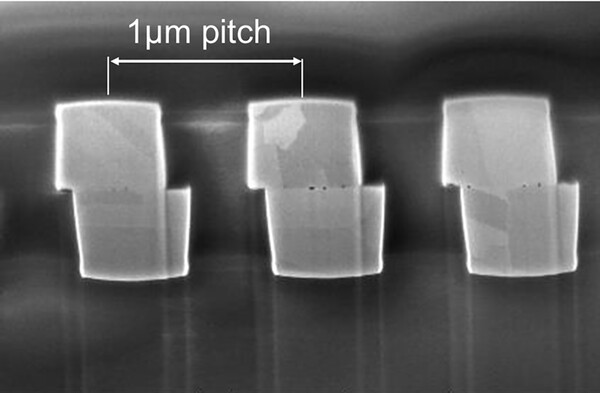

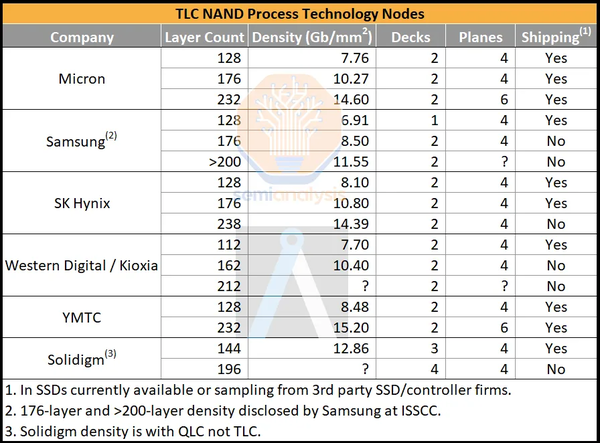

YMTC는 엑스태킹 기술을 이용해 공정 효율을 개선할 수 있고, 칩 밀도 역시 높일 수 있다고 강조한다. 실제 시장조사업체 세미애널리시스에 따르면 지난해 YMTC가 발표한 232단 3D 낸드플래시 제품(X3-9070)은 1㎜² 당 저장용량이 15.2Gb로 측정됐다. 이는 비슷한 시기 232단 제품을 발표한 마이크론(14.6Gb/㎜²), 238단 제품을 발표한 SK하이닉스(14.39Gb/㎜²) 보다도 높은 수준이다.

최정동 테크인사이트 박사는 “마이크론⋅SK하이닉스는 200단 이상 제품이 시장에서 거의 구할 수 없는데 비해 YMTC 232단은 쉽게 발견된다”며 “YMTC의 200단 이상 제품 양산 기술이 그만큼 안정화 됐다는 의미”라고 설명했다. 테크인사이트는 시중에 판매되는 반도체 제품을 구입해 ‘리버스 엔지니어링(역설계)’ 방식으로 분석하는 회사다.

한 반도체 산업 전문가는 “PUC⋅COP 방식은 수백단의 셀을 올리는 동안 셀 아래 위치한 주변부 회로가 열적⋅물리적 스트레스를 상당히 많이 받는다”며 “이 때문에 주변부 회로를 보호하기 위한 공정 제약이 크다”고 말했다. 하이브리드 본딩 기술을 쓴다면 이 같은 제약 없이 공정을 진행할 수 있다.

웨이퍼 가격 및 하이브리드 본딩 공정 구축은 부담

이 같은 장점에도 불구하고 삼성전자⋅SK하이닉스⋅마이크론이 아직 관련 기술을 도입하지 않은 건 높아지는 비용 때문이다.

우선 단순히 계산해도 낸드플래시 다이 1개를 생산하는데 필요한 웨이퍼 수가 2배로 늘어난다. 이는 SK실트론 같은 웨이퍼 공급 업체에는 호재지만, 가뜩이나 마진폭이 작은 낸드플래시 업계로서는 부담이다.

하이브리드 본딩 공정 구축을 위한 설비투자도 필요하다. 현재 하이브리드 본딩 장비는 오스트리아 EV그룹과 일본 도쿄일렉트론 정도만 공급 가능하다. 그나마도 EV그룹이 80% 이상 시장점유율로 독점력을 행사하고 있다. 장비 도입 가격이 비쌀 수 밖에 없다.

특허 문제도 풀어야 한다. YMTC의 엑스태킹은 미국 엑스페리의 특허 라이선스를 통해 개발됐다. 삼성전자⋅SK하이닉스⋅마이크론도 자체 기술을 개발하지 않는 이상 엑스페리와의 라이선스가 필요하다. 이 역시 코스트 증가 요인으로 작용한다.

삼성전자⋅SK하이닉스는 3D 낸드플래시가 아닌 CIS 생산에 이미 하이브리드 본딩 기술을 쓰고 있다. 그러나 CIS 웨이퍼는 낸드플래시 웨이퍼 대비 휨(Warpage) 현상이 적고, 연결해야 하는 패드(패턴) 사이즈도 크다. 상대적으로 난이도가 낮다. CIS에서 하이브리드 본딩 공정을 해 봤다고 해서 3D 낸드플래시 공정에서 바로 수율을 끌어올리는 건 불가능하다. 공정 추가에 따른 수율 안정화 비용도 감안해야 한다.

또 다른 반도체 산업 전문가는 “메모리 3사가 3D 낸드플래시 생산에 하이브리드 본딩 기술을 도입하는 건 시간문제”라며 “300단 이상으로 진보하기 위해 어차피 하이브리드 본딩을 써야 한다면, 먼저 도입해서 경험치를 쌓는 게 이득일 수 있다”고 말했다.