시생산과 샘플 납품 등 진행 중

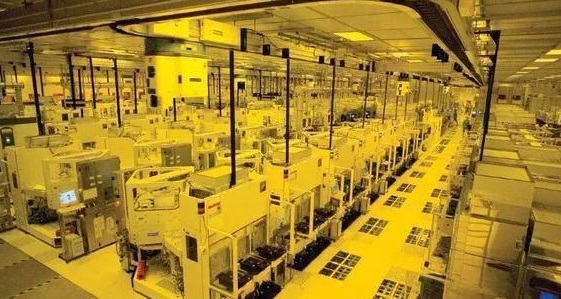

TSMC가 5nm 공정이 시생산 단계에 진입했다고 밝혔다.

4일 TSMC는 이같은 내용을 발표하면서 개방형 혁신 플랫폼을 기반으로 5nm 아키텍처 제품을 출시, 고객과 협력해 차세대 첨단 모바일, 고효율 연산 애플리케이션 제품의 5nm 시스템 싱글칩 설계를 구현했다고 설명했다. 목표 시장은 가파르게 성장하는 5G와 인공지능(AI) 영역이다.

TSMC의 5nm 공정 시생산 제품은 차세대 하이엔드 모바일 및 고효율 연산 애플리케이션 제품으로서 7nm 공정과 비교할 때 ARM 코어텍스(Cortex) A72 코어 집적도를 높여 1.8배의 로직 밀도를 제공, 속도를 15% 높였다고 전했다. 이전 공정 아키텍처와 비교할 때 성능좋은 SRAM과 아날로그 면적 축소가 이뤄졌다.

TSMC는 5nm 공정이 극자외선(EUV) 기술을 통해 공정 효율을 단순화했다고 전했다. 이전 공정과 비교할 때 같은 단계의 경우 기술 성숙도가 높아졌다. 업계 최대의 설계 공급망 자원과 고객 협력을 통해 상품을 설계 및 시생산, 그리고 초기 샘플 납품이 양호하게 이뤄지고 있다는 설명이다.

TSMC의 연구개발 및 기술발전 허우융칭(侯永清) 부총경리는 “5nm 기술을 통해 고객에게 가장 선진적인 로직 공정을 제공할 수 있으며 인공지능과 5G가 접목된 더 강력한 연산 기능 수요에 대응할 수 있게 됐다”고 말했다. 또 “설계 생태계 시스템 파트너들과 긴밀한 협력을 통해 고객 수요에 대응할 때 검증된 실리콘(Silicon) IP 조합과 설계 자동화 툴을 제공할 수 있다”고 덧붙였다.

TSMC는 케이던스(Cadence), 시놉시스(Synopsys), 멘토그래픽스(Mentor Graphics), 앤시스( ANSYS) 등 설계 파트너와 협력으로 개방형 혁신 플랫폼 전자 설계 자동화 검증 솔루션을 통해 전자 설계 자동화 툴 검증을 진행하면서 고객이 TSMC의 5nm 공정 기술을 활용할 수 있도록 지원하겠다고 밝혔다.