고객 시제품 납품 및 수율·캐파 ↑

중국 창신메모리(CXMT)가 올 상반기 내 17nm 공정 DDR5 시제품을 내놓는다.

중국 언론 신즈쉰이 인용한 대만 언론에 따르면 허페이(合肥) 창신메모리가 올해 2분기 17nm 공정 DDR5 칩을 시생산하고 동시에 생산능력 확장을 모색한다.

최근 창신메모리의 허페이 법인인 허페이창신의 17nm 공정 DDR 칩 수율이 이미 40%에 도달했으며, 올해 2분기 시생산해 시제품을 고객에 인도할 것이란 예상이다. 비록 40%의 수율이 비교적 낮은 편이지만, 창신메모리는 뒤이어 수율을 지속적으로 높인다는 계획이다.

창신메모리의 모회사인 루이리지청(睿力集成)이 올해 2월 330억 위안 규모 투자를 받은 데 이어진 소식이다.

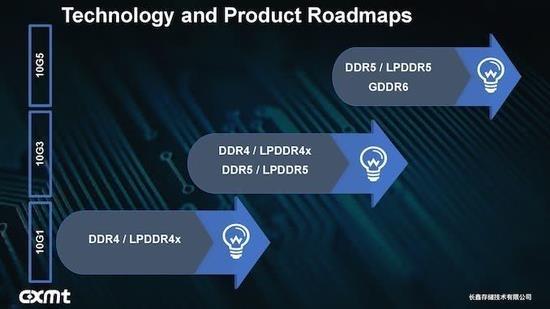

앞서 창신메모리가 밝힌 로드맵에 따르면, 17nm DDR5/LPDDR5를 출시한 이후 10nm 공정 상품을 출시할 예정이다.

생산능력 측면에서 앞서 창신메모리는 2020년, 2021년 각각 월 4만5000장, 월 6만 장의 생산능력을 목표로했으며, 올해 생산능력 목표치는 월 12만 장이다. 향후 월 30만 장까지 늘릴 계획이다.

시장조사업체 트렌드포스 예측에 다르면 지난해 말 글로벌 메모리 생산능력은 월 150만 장이였으며, 이중 삼성전자의 생산능력이 월 55만5000장을 넘고, SK하이닉스는 월 36만 장, 마이크론은월 35만5000장이였다. 아직 창신메모리의 D램 생산능력은 상위권 기업과 격차가 있다.

또 기술 측면에서 삼성전자는 이미 14nm 극자외선(EUV) 공정의 LPDDR5를 양산해 창신메모리의 17nm 공정 DDR5/LPDDR5와도 1~2세대의 기술 격차가 있다.