칩 쪼개면 미세공정 도입에 따른 비용 상쇄

치플렛 연결 위한 FC-BGA는 2026년 수급 안정

괴물 같은 전성비(전력대 성능비)를 보여준 애플 ‘M1 울트라’는 ‘M1 맥스’를 두 개 이어붙인 제품이다. 반도체 성능은 결국 얼마나 많은 트랜지스터를 내장했는지에 비례하는데, 애플은 고성능 칩 2개를 기워 정확히 두 배 성능의 반도체를 만들었다.

주목할 건 애플이 처음부터 M1 울트라 크기의 실리콘 칩을 만들지 않았다는 점이다. 애플은 왜 두 개의 칩을 각각 따로 만들어 연결하는 수고를 택했을까.

한계에 봉착한 미세공정의 경제성

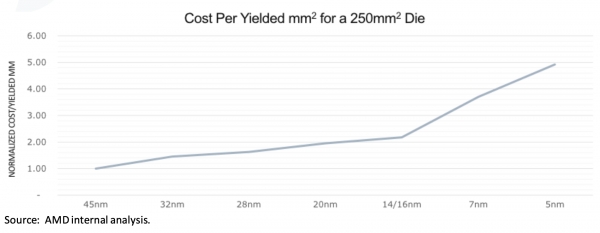

AMD 내부 분석에 따르면 250㎜² 크기의 칩을 만든다고 가정했을 때, 20nm(나노미터) 공정으로 제조하면 1㎜² 당 가격은 2달러 정도다. 미세공정 수준을 높여 14nm를 써도 단가는 2달러대 초반에 그친다. 그러나 10nm 벽을 깨고 7nm로 내려오면 생산단가는 3달러 후반, 5nm는 5달러로 치솟는다.

14m까지는 공정 업그레이드에 따른 단가 부담이 크지 않았으나 7nm부터는 채산성이 급격히 나빠지는 것이다. 이는 7nm부터 일부 EUV(극자외선) 노광장비가 도입되고, EUV가 아니더라도 멀티패터닝 스텝수가 늘면서 팹 투자비와 생산비용이 기하급수적으로 증가하기 때문이다.

이처럼 미세공정에 따른 비용 부담이 가중되는 상황에서 반도체 생산비를 조금이라도 줄이려면 어떻게 해야 할까. 애플을 비롯해 최근 반도체 업계가 내린 결론은 ‘치플렛(Chiplet)’ 생산방식의 확대다.

치플렛은 단어 그대로 반도체 칩(Chip)을 잘게 쪼갠 제품이다. 처음부터 ‘빅 칩(Big Chip)’을 만드는 대신, 기능들을 분산해 여러개의 칩으로 나눠 만든 것이다. 애플이 M1 맥스 두 개를 붙여 M1 울트라를 만든 게 대표적인 치플렛 방식 생산이다.

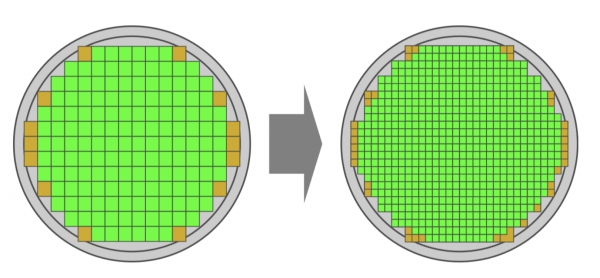

단일 실리콘 칩을 크게 만드는 것과 비교하면 치플렛 방식은 수율을 크게 높여 생산 비용을 절감할 수 있다. 기본적으로 반도체를 생산하는 웨이퍼는 원형이다. 이를 사각형 칩으로 잘라 쓰는데, 사각형 가로⋅세로 길이가 길어질수록 엣지(테두리) 부위에 버려야 하는 면적이 넓어진다. 반대로 칩 사이즈가 줄어들면 그 만큼 아깝게 폐기되는 면적을 줄일 수 있다. 불량칩이 발생한 경우를 가정해도, 개별 칩 크기가 작을 때의 손실이 더 적다.

새로운 디자인 검증에 따른 부담이 절감되는 것도 치플렛 방식의 장점이다. CPU를 예로 들면, I/O(Input/Output)처럼 여러 제품에 공통적으로 사용되는 부위는 새로 디자인하지 않고 디자인을 재사용할 수 있다. 신제품 개발시 모든 기능들을 새로 디자인하는 것과 비교하면 검증을 위한 비용을 크게 절감할 수 있다.

나정주 인텔코리아 상무는 “디자인 검증 부담이 줄어든다는 건 단순히 비용절감 뿐만 아니라 시장에 제품을 적기 출시할 수 있게 만들어준다는 의미”라고 말했다.

치플렛 핵심은 상호 연결

이처럼 단일 칩으로 만들때보다 수율과 비용 측면에서 유리하다 보니 반도체 업계는 치플렛 방식 생산을 확대하고 있다. AMD는 이미 데스크톱과 서버용 CPU 생산에 치플렛 기술을 도입했다. 최대 8개의 컴퓨팅 치플렛과 1개의 I/O 치플렛을 상호 연결해 하나의 CPU를 구성한다. 인텔은 올해 하반기 출시될 서버용 CPU ‘사파이어래피즈’에 처음 치플렛 기술을 적용할 예정이다.

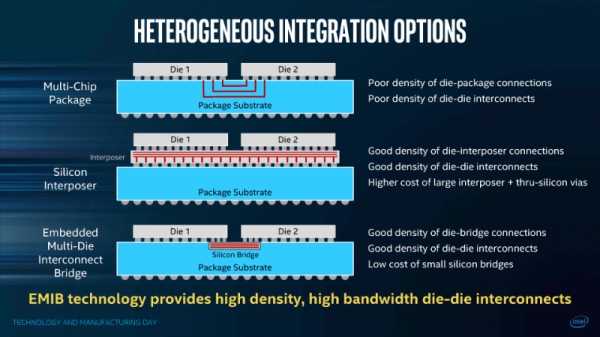

최근 2.5D 패키지 기술이 부각되고, 2.5D 패키지를 위한 부품인 FC-BGA(플립칩-볼그리드어레이) 공급난이 극심해 진 것도 치플렛 방식 생산 증가 때문이다. 치플렛으로 분산된 기능들을 상호 연결하는데 MCM(멀티칩모듈)⋅3D 패키지 등 다양한 방법이 있지만, FC-BGA를 이용한 2.5D 패키지가 가장 효율적이다.

2.5D 패기지는 각 치플렛을 수평 방향으로 배치하면서도 3D 패키지에 맞먹는 대역폭을 구현할 수 있다. 이를 위해 각 치플렛을 연결하는 FC-BGA가 필수다. 인텔의 EMIB(Embedded Multi-Die Interconnect Bridge)나 AMD의 EFB(Elevated Fanout Bridge)도 FC-BGA를 이용한 2.5D 패키지 기술이다.

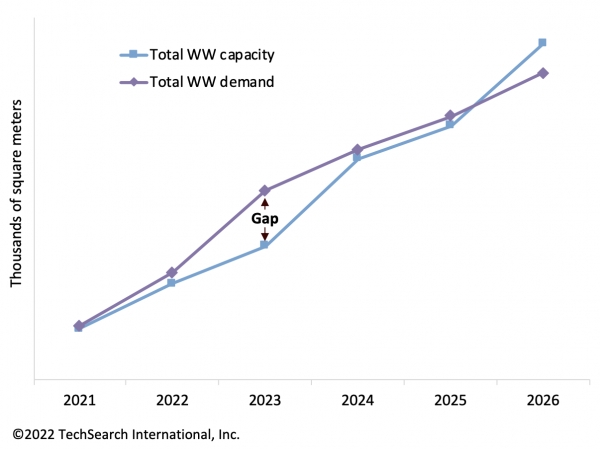

시장조사업체 테크서치에 따르면 FC-BGA 공급난은 올해보다 내년이 더 극심할 전망이며, 오는 2026년쯤에나 공급량이 수요를 초과할 것으로 예상된다. 잰 바더만 테크서치 대표는 최근 SEMI(국제반도체장비재료협회) 심포지엄에서 “FC-BGA 업체들의 생산능력 투자분이 2024년 이전까지 산입되지 않을 것”이라며 “이 때문에 FC-BGA 수급난은 2025년까지 해소되기는 어렵다”고 설명했다.