기존의 절반 수준으로 줄여...장기적으로 0.4μm까지

이론적으론 L/S 좁히면 저항 높아져 신호 전송 효율 저하

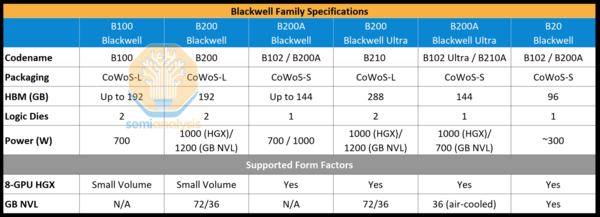

TSMC가 2.5D 패키지 기술인 CoWoS-L을 선보이면서 배선 L/S(라인앤드스페이스, 배선폭)를 기존의 절반 수준으로 축소한 것으로 파악됐다. CoWoS-L은 종전 CoWoS-S 대비 실리콘 매개체 면적이 좁은 탓에 L/S를 줄여 GPU-HBM을 연결을 욱여넣은 것으로 추정된다.

그동안 GPU와 HBM을 고속 연결하기 위해서는 적정 수준의 배선폭을 유지해야 한다는 게 정설이었다.

CoWoS-L, L/S 0.8~1.2μm로 축소

TSMC가 CoWoS-S에서 GPU와 HBM을 연결하기 위해 쓴 배선의 L/S는 2/2μm였다. L/S가 2/2μm라는 건 구리 배선의 두께와 배선간의 빈공간이 2μm라는 뜻이다. 이 배선을 통해 GPU와 HBM이 신호를 주고 받는다.

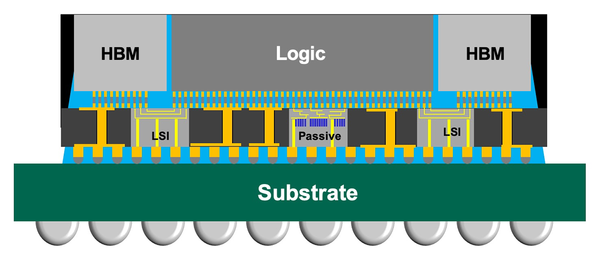

TSMC는 이를 CoWoS-L로 바꾸면서 배선 L/S를 0.8~1.2μm 수준으로 축소했다. CoWoS-L은 CoWoS-S에서 사용하던 실리콘 인터포저를 실리콘 브릿지로 대체한 기술이다. 원래 GPU와 HBM 전체를 덮고도 남을 정도로 큰 실리콘 인터포저를 쓰다가 GPU-HBM 연결부만 커버할 정도의 작은 실리콘 조각(브릿지)으로 바꾼 것이다.

GPU와 HBM을 연결하는 매개체의 면적이 줄어들다 보니 배선 L/S도 좁아질 수 밖에 없다. 지하주차장 전체 면적이 줄어들면 자동차 한 대에 할당하는 공간은 좁아지는 것과 같은 이치다.

한 반도체 산업 전문가는 “TSMC는 CoWoS-L에서 L/S를 0.8~1.2μm 수준으로 좁혔는데 장기적으로 0.4μm까지 축소한다는 로드맵을 갖고 있다”고 말했다.

L/S 축소와 신호 전달, ‘두 마리’ 토끼 어떻게 잡았나

다만 그동안 반도체 업계는 GPU와 HBM 간 연결은 배선폭을 아무리 줄여도 2μm 아래로 내려가는 건 위험성이 크다는 의견이 대세였다. 두 반도체 사이에 워낙 많은 데이터 전송이 이뤄지기 때문에 적정 L/S를 유지해야 한다는 이유에서다. 배선폭이 줄어들면 반대로 저항은 커지고, 이는 신호 손실로 귀결된다. AI(인공지능) 학습을 위해 늘 고대역 송수신이 이뤄지는 2.5D 패키지에 적용하기에는 특히 리스크가 높다.

이 때문에 내년에 나올 HBM4 규격을 위해 L/S를 2/2μm 아래로 내리는 대신 GPU-HBM을 연결하는 실리콘 인터포저(혹은 브릿지) 단수를 높여 신호를 연결하는 방안도 타진돼 왔던 터다. 지하주차장을 4층으로 운용하던 것을 8층으로 깊게 파면 같은 면적에 더 많은 자동차를 주차할 수 있는 것과 같은 이치다.

현재 HBM3E에는 1024개의 입출력 단자가 있고, 이를 연결하기 위해 총 4단 레이어가 배치된다. 각 레이어에는 512개씩의 비아홀이 형성되며, 2개층이 신호를, 다른 2개층이 전력을 전송하는 역할이다. 만약 이를 8개층으로 늘릴 수 있다면 각 층에 256개의 비아홀만 배치하면 된다. 공간상 여유가 생기는 것이다. 이는 향후 입출력 단자가 2048개로 2배 늘어날 HBM4 규격에서 L/S를 축소하지 않고 GPU-HBM을 연결하는 방식이 될 수 있다.

그러나 TSMC는 이처럼 실리콘 브릿지 단수를 늘리지 않고도 L/S를 2/2μm 이내로 축소하는 접근법으로 GPU-HBM을 연결했다. 다시 지하주차장 비유에 대입하면 주차장 깊이를 더 파지 않고, 자동차 한 대에 할당되는 공간을 최대한 줄이고 낭비되는 면적까지 활용하는 방식으로 배선폭을 줄인 것이다.

또 다른 반도체 산업 전문가는 “실리콘 매개체 단수를 높이면 L/S를 줄이지 않고 GPU-HBM을 연결할 수 있으나 대신 인터포저의 휨 문제가 더 커지는 등 부가적인 이슈가 발생하게 된다”며 “TSMC가 어떻게 배선폭을 줄이면서도 어떻게 신호 뭉개짐 없이 GPU-HBM을 연결했는지가 관건”이라고 말했다.

한편 TSMC는 이 때문에 실리콘 브릿지를 내 배선을 계측하기 위한 새로운 방식도 도입한 것으로 알려졌다. 앞서 TSMC는 WLI(백색광간섭계)를 이용해 배선을 계측했으나, 실리콘 브릿지 내 L/S를 줄이면서는 AFM(원자현미경) 방식으로 변경한 것으로 전해졌다.