삼성 파운드리가 쓰는 23개 툴 공급업체 중 하나

"2025년 내 미국 EDA 툴 대체 목표"

반도체 회로 패턴을 그리는 노광장비는 중국 반도체 산업의 가장 큰 아킬레스건으로 꼽힌다. 네덜란드 ASML의 노광장비 없이는 14nm(나노미터) 이후의 미세 회로 패턴을 그릴 방법이 없다. 여기에 미국이 쥐고 있는 중국 반도체 견제 장치가 하나 더 있다. 바로 반도체 EDA(설계자동화) 툴이다.

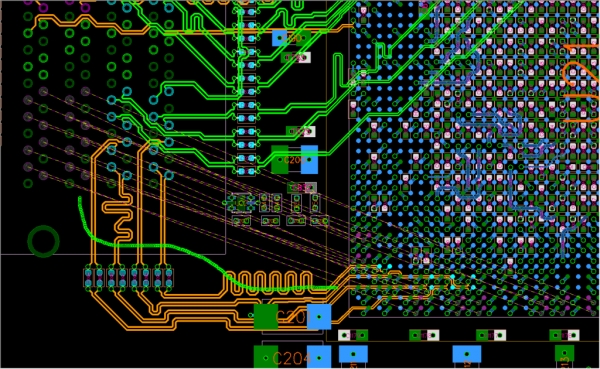

노광장비가 설계도에 따라 반도체를 만드는 도구라면, EDA 툴은 설계도 자체를 그리는 연필이다. EDA 툴 시장에서 중국의 자급률은 2%가 채 안 된다.

중국 3대 EDA 툴 회사, 임피리언

시장조사업체 트렌드포스에 따르면 전 세계 EDA 툴 시장 점유율(2021년 기준)은 시놉시스가 32%, 케이던스 30%, 지멘스 13% 정도다. 이 중에 1⋅2위인 시놉시스⋅케이던스가 미국 회사다. 미국 상무부는 지난해 8월 우선 차세대 시스템 반도체 구조인 GAA(게이트올어라운드) 기반 반도체 설계에 필요한 EDA 툴 수출 규제를 발효했다.

GAA는 삼성전자가 3nm부터, 대만 TSMC가 2nm 제품부터 적용하는 기술이다. 아직 중국 SMIC는 7nm 양산 비중도 극히 일부라는 점에서 EDA 툴 수출 규제 수준이 높다고는 볼 수 없다. 현재의 EDA 툴 수출 규제로 중국이 받는 타격은 미미하다는 뜻이다. 그러나 경우에 따라서는 SMIC가 메인으로 쓰고 있는 핀펫(FinFET) 설계용 EDA 수출을 통제하는 방식으로 언제든지 규제 허들을 높일 수도 있다.

중국 임피리언테크놀러지(이하 임피리언)는 X-에픽, 셀릭스소프트와 함께 이 같은 난국을 타개하기 위해 정부의 전폭적인 지원을 받고 있는 EDA 툴 회사 중 회사다. 임피리언은 최근 AI(인공지능)를 활용한 설계 자동화와 칩렛(Chiplet) 패키지를 지원할 수 있는 EDA 툴 연구개발에 착수했다.

웨이핑류 임피리언 회장은 중국 매체 아이지웨이와의 인터뷰에서 “중국 EDA 툴 산업이 과거 대비 발전하기는 했지만, 여전히 반도체 설계에 필요한 솔루션의 70%만 공급해 줄 수 있다”며 “AI가 선두 업체들과의 격차를 줄여주는 도구가 될 것”이라고 말했다.

이미 글로벌 EDA 툴 회사들은 지난 2020년 이전부터 반도체 설계와 검증 분야에 AI 기술을 적용했다. 반도체 설계시 오류를 야기하는 각종 버그를 AI 기술로 신속하게 파악해 미리 해결할 수 있다. SoC(시스템온칩) 설계에 필요한 각종 IP(설계자산)과 소스코드를 비교해 오류 잠재성을 정확히 찾아내는 알고리즘도 공급한다. 이를 통해 반도체 설계에 소요되는 시간과 비용을 획기적으로 절감할 수 있다.

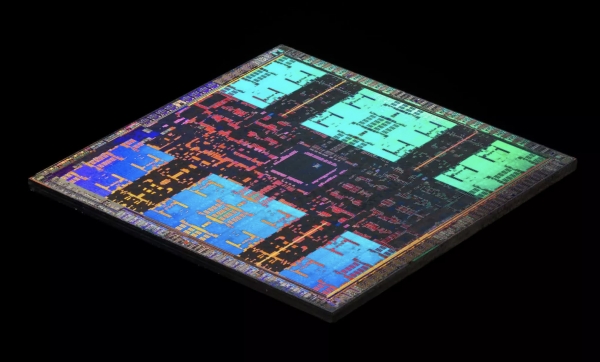

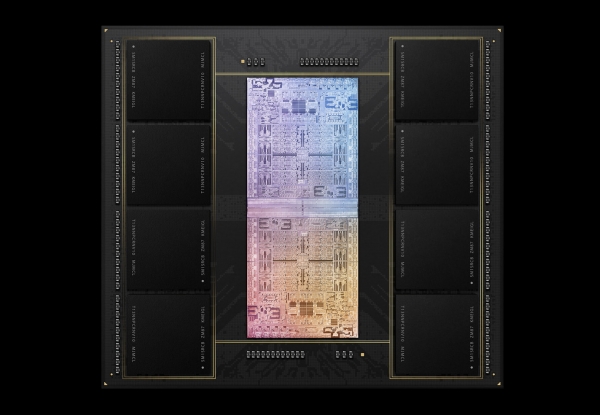

임피리언이 R&D(연구개발)를 시작한 칩렛 디자인 역시 최근 반도체 업계의 화두다. 칩렛은 반도체 다이 사이즈를 키우지 않고, 반도체를 기능별로 잘게 쪼개 패키지 단계에서 이어 붙이는 기술이다. 7nm부터는 다이 사이즈 확대에 따른 생산비용이 기존 14nm의 두배, 5nm부터는 2.5배로 증가한다. 칩렛 방식을 적용하면 ‘빅 칩(Big Chip)’을 만드는 대신 기능들을 분산하는 방식으로 생산원가를 절감할 수 있다. 애플이 ‘M시리즈’ 칩 2개를 이어 붙여 ‘울트라’를 만드는 게 대표적인 칩렛 생산 방식이다.

임피리언, 벌써 시가총액 9조원

물론 웨이핑류 회장의 지적처럼 실제 파운드리 업계에서 임피리언이 갖는 위상은 높지 않다. 예컨대 현재 삼성전자 파운드리 사업부가 쓰는 EDA 툴은 23개로, 그 중 8개를 중국 업체가 공급한다. 임피리언은 이 8개 중의 하나다. 그러나 임피리언을 포함한 중국 회사들의 EDA 툴 공급가는 글로벌 업체들 대비 턱 없이 낮으며, 실제 칩 설계에 동원되는 레이어도 많지 않은 것으로 알려졌다.

중국 EDA 자급률이 2%에 그친다는 통계도 있다. 중국의 반도체 자급률(중국 내 해외업체 제외)은 6% 남짓으로 추정되는데, EDA 자급률은 이에도 미치지 못하는 셈이다.

한 반도체 설계 전문가는 “SoC 설계 인력의 대부분이 시놉시스⋅케이던스⋅지멘스 설계 툴로 전공하고, 현업에서 활동하고 있다”며 “솔루션 특성상 손에 익지 않은 도구를 써줄 회사는 많지 않을 것”이라고 말했다.

다만 중국 정부가 EDA 툴 자립에 전폭적인 지원을 하고 있고, 임피리언이 그 선두라는 점에서 중국 반도체 업계가 거는 기대는 크다. 이 회사는 지난해 7월 중국 상하이 증시에 입성했는데, 현재 시가총액만 482억위안(약 9조원)에 이른다. 임피리언은 상장 당시 증권 신고서에서 2025년까지 해외 EDA 툴을 완전히 대체하고, 2030년까지 관련 시장에서 선두가 되겠다는 목표를 밝힌 바 있다.