ASD, 웨이퍼 위 특정 영역만 증착하는 기술

14nm 코발트 증착에 가장 먼저 사용

“향후 반도체 공정 미세화가 진행될수록 ALD(원자층증착) 기술 도입이 늘텐데 그 중에서도 특정 영역에 선택적으로 증착하는 ASD(Area-Selective Deposition) 적용 범위가 증가할 것입니다.”

18일 SEMI(국제반도체장비재료협회)가 주최한 ‘전략재료컨퍼런스(SMC)’에서 조윤정 삼성전자 마스터는 ASD 기술과 그에 대응하는 신소재 개발 필요성을 역설했다.

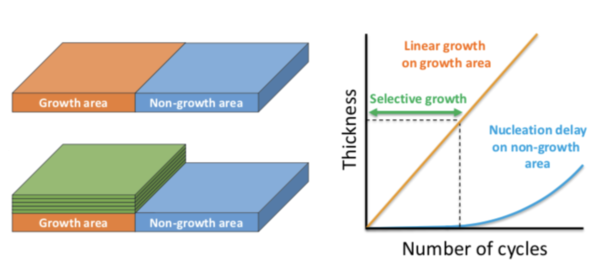

ASD는 ALD의 한 종류로, 웨이퍼 특정 영역에만 선택적으로 성막할 수 있는 공정 기술을 뜻한다. 예컨대 A자 형태의 패턴이 필요하다면, 기존 ALD는 웨이퍼 전 영역에 골고루 박막을 입힌 뒤 필요 없는 부분을 식각으로 긁어내 A자 패턴을 만든다. 이 과정에서 노광⋅현상 같은 포토리소그래피 공정들이 다 같이 동원되어야 함은 물론이다.

ASD는 처음부터 A 패턴을 형성하는데 필요한 부분에만 물질이 증착됨으로써 간단하게 패턴을 완성할 수 있다. 그만큼 생산 효율이 향상된다. 증착에 사용되는 프리커서(전구체)의 양을 획기적으로 절감할 수도 있다. 굳이 불필요한 부위까지 증착하지 않아도 되기 때문이다.

조 마스터는 “현재 낸드플래시에 이어 D램과 로직반도체까지 3D 적층구조로 전환하는 방안이 연구되고 있다”며 “ASD 기술은 2D 보다는 3D 적층 구조 반도체 생산에서 파워풀할 것”이라고 설명했다.

반응 가스에 의해 막을 입히는 과정에서 선택적 증착 현상이 일어나는 건, 이종 기판 간에 결정핵생성(Nucleation) 시간차가 발생하기 때문이다. 사전에 웨이퍼 위에 어떤 물질이 올라가 있느냐에 따라 그 위에 새로운 물질이 성막되는데 걸리는 시간이 다르다는 의미다. 이 시간차를 극대화하거나, 억제재(Inhibitor)를 적절하게 사용하면 특정 물질 위에만 성막하는 게 가능하다. 혹은 프리커서의 리간드(Ligand)를 컨트롤함으로써 ASD 성능을 높일수도 있다.

조 마스터는 “ASD 막을 입힐 표면(Surface)에 대한 연구가 선행되어야 하며, 억제재가 특정 공정 조건에서 어떻게 반응하는지에 대한 충분한 데이터베이스가 갖춰져야 할 것”이라고 말했다.

ASD 기술에 대한 연구가 반도체 업계서 시작된 것은 약 20년 전이다. 실제 양산에 적용된 것은 로직반도체가 제일 처음으로, 14nm(나노미터) 공정 중 코발트 증착에 ASD 기술이 첫 적용됐다. 현재도 극히 일부 공정에만 적용되고 있으며, 향후 3D 적층구조 반도체 생산에 확대 적용될 것으로 예상된다.