[The Korea Industry Post(kipost.net)] 반도체 화학적기계연마(CMP) 공정 제조 시간과 비용을 획기적으로 줄일 수 있는 텅스텐(W) CMP 슬러리를 국내 중소기업이 개발했다. 두 개로 나뉘었던 기존 공정을 일원화 할 수 있어 슬러리와 패드 공급 시장 판도도 변화할 전망이다.

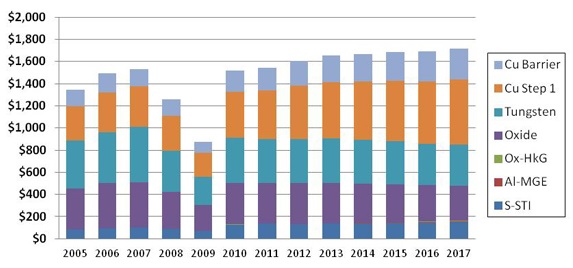

CMP는 적층형 반도체를 제조할 때 거의 필수적으로 거치는 공정으로, 반도체가 3차원화 되면서 점점 쓰임새가 늘고 있어 외산 소재 업체는 물론 국내 소재·장비사도 속속 뛰어들고 있는 시장이다.

13일 업계에 따르면 SK하이닉스는 이르면 이번 하반기 국내 중소기업 유비머트리얼즈가 개발한 텅스텐 CMP 슬러리를 도입할 예정이다. 기존 텅스텐 CMP 공정은 1·2차로 나뉘었는데 신소재를 쓰면 2차 공정 없이 다음 단계로 넘어갈 수 있다.

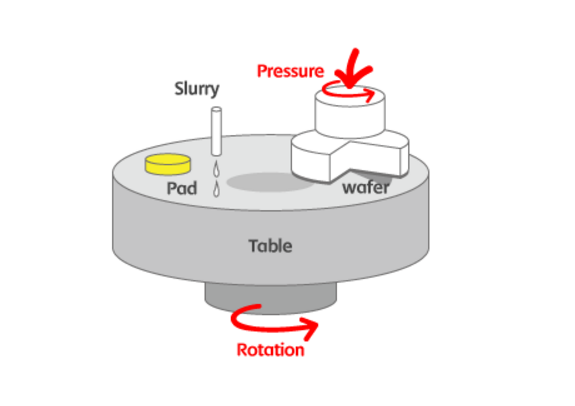

다양한 화학물질과 금속을 쌓을 때 하나의 물질을 증착한 다음에는 평탄화 과정을 거친다. 이 때 주로 쓰이는 게 식각(에칭) 또는 CMP 공정이다. 평탄화 공정을 거치지 않을 경우 물질의 표면에 울퉁불퉁한 단차가 생겨 적층 구조가 무너진다. CMP는 웨이퍼 전 표면을 매끈하게 만들어주기 때문에 활용도가 점점 더 커지고 있다.

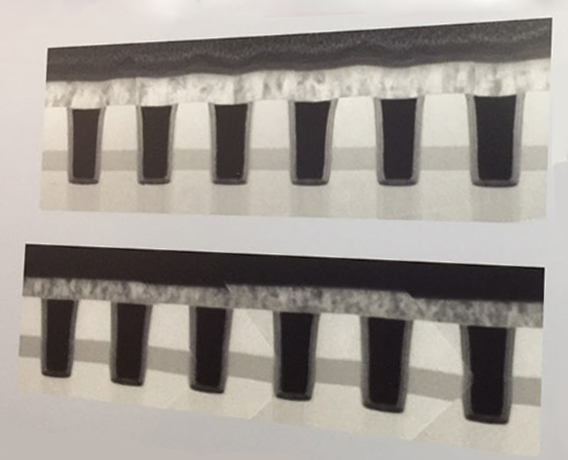

텅스텐은 전극으로 쓰이는 주요 소재다. 작은 구멍(홀)을 뚫은 다음 화학기상증착(CVD), 원자층증착(ALD) 방식으로 텅스텐 층을 형성하는데, 전극 부분을 제외한 부분은 걷어내야 한다. 문제는 기존 텅스텐 CMP 공정을 거치더라도 디싱(dishing, 살짝 파인 부분)이 생겨 표면 단차가 여전히 존재한다는 점이다. 이 때문에 디싱 결함(Dishing Defect)을 없애는 옥사이드(Oxide) CMP 공정이 추가된다.

유비머트리얼즈가 개발한 텅스텐 슬러리로 연마를 할 경우 디싱 결함은 수옴스트롱(Å) 수준으로 줄어들어 2차 공정을 없앨 수 있다.

공정 감소가 가져오는 시장 변화

텅스텐은 금, 알루미늄 등과 더불어 배선의 주요 소재로 쓰이는데, 알루미늄이 진공증착(이베포레이션), 플라즈마 물리 기상증착(스퍼터링) 방식을 사용하기 때문에 좁은 홀은 채우기 힘들다. 이 때문에 반도체가 미세 공정으로 이행할수록 텅스텐 사용량이 많아진다.

텅스텐 슬러리 시장은 미국 캐보트가 장악하고 있다. 삼성SDI(구 제일모직), 동진쎄미켐이 특허소송에서 승소해 일부 공급한다. 2차 공정용CMP 슬러리 공급사는 솔브레인, 동진쎄미켐 등이 포진한다.

실제로 유비머트리얼즈의 소재가 채택되면 캐보트를 대체해 국산화해 소자 기업의 협상력도 높일 수 있다. 다만 2차 공정용 CMP를 공급하던 업계는 다소 타격이 불가피하다.