Combining massively parallel architecture of an FPGA with OpenCL parallel programming model, the SDK allows system developers and programmers familiar with C language to quickly and easily develop high-performance, power-efficient FPGA-based applications in a high-level language.

The Altera SDK for OpenCL enables FPGAs to work in sync with the host processor to accelerate parallel computation, at a fraction of the power compared to hardware alternatives.

"The industry's approach for boosting system performance has evolved over time from increasing frequency in single-core CPUs, to using multi-core CPUs, to using parallel processor arrays," said Vince Hu, vice president of product and corporate marketing at Altera. "This evolution leads us to today's modern FPGAs, which are fine-grained, massively parallel digital logic arrays architected to execute computations in parallel. Our SDK for OpenCL enables customers to easily adopt FPGAs and leverage the performance and power benefits the devices provide."

The Altera SDK for OpenCL offers a unified, high-level design flow for hardware and software development that automates the time-consuming tasks required in typical hardware-design language (HDL) flows.

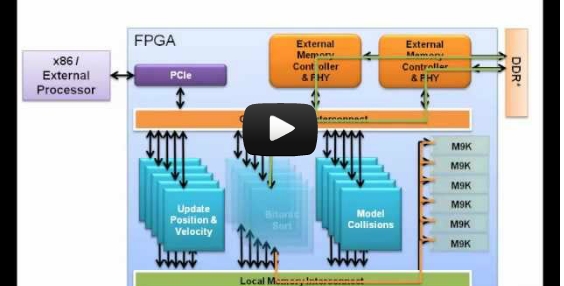

The OpenCL tool flow automatically converts OpenCL kernel functions into custom FPGA hardware accelerators, adds interface IPs, builds interconnect logic and generates the FPGA programming file.

The SDK includes libraries that link to OpenCL API calls within a host program running on the CPU. By automatically handling these steps, designers are able to focus their development efforts on defining and iterating their algorithms rather than designing hardware.

The portability of the OpenCL code enables users to migrate their designs to different FPGAs or SoC FPGAs as their application requirements evolve. With SoC FPGAs, the CPU host is embedded into the FPGA, providing a single-chip solution that delivers significantly higher bandwidth and lower latency between the CPU host and the FPGA compared to using two discrete devices.