미하우 시윈스키(Michał Siwiński) 케이던스 마케팅 및 사업 개발 부사장 인터뷰

반도체 설계자동화(EDA) 툴은 반도체 설계부터 전·후공정까지 반도체 제조의 전 과정에서 쓰이는 도구다. 아무리 좋은 공정 기술이 개발됐다 해도 이를 지원하는 EDA 툴이 없다면 무용지물이다.

최근 EDA 업계는 반도체 생태계 내 어떤 섹터보다 바쁘게 움직이고 있다. 기술 개발의 중심이 전공정에서 설계·제조 전반으로 확장되면서 지원해야하는 영역이 그만큼 넓어졌기 때문이다.

무어의 법칙을 넘어 모어 댄 무어를 실현하기 위해 이들은 어떤 노력을 하고 있을까. EDA 업계 2위 케이던스(Cadence Design Systems)에서 마케팅 및 사업 개발을 총괄하고 있는 미하우 시윈스키(Michał Siwiński) 부사장에게 물었다.

하나. 제조 기술의 한계를 넘다 - 후공정

핀펫(FinFET) 기술로 14·16나노의 장벽이 무너졌을 때 업계는 이 공정이 꽤나 오랜 시간 첨단 공정 기술로 자리잡을 것이라 예측했다. 더 이상의 기술 발전은 어렵다고 판단했기 때문이다.

미하우 시윈스키 부사장은 “사실상 그때부터 ‘모어댄무어’가 시작됐다”며 “(업계는) 트랜지스터 크기를 물리적으로 축소시키는 것만으로는 무어의 법칙을 현실화할 수 없다는 걸 깨달았다”고 말했다.

이에 반도체 업계는 그때부터 첨단 후공정(Advanced Package) 연구개발(R&D)을 시작했다. TSMC가 팬아웃(Fan-out) 웨이퍼레벨패키지(WLP) 기술 개발을 시작한 것도 이 즈음이다.

첨단 후공정은 반도체와 패키지 기술을 융합해야 한다. 즉, EDA 업계 입장에서는 반도체와 패키지 도구를 각각 이에 맞춰 내놔야한다. 케이던스는 이때부터 TSMC 등 파운드리 업체와 협력, 첨단 후공정 관련 EDA 툴을 개발했다. 현재도 대부분의 첨단 패키지가 케이던스의 EDA 툴로 만들어진다.

둘. 제조 기술의 한계를 넘다 - 전공정

업계의 예상을 깨고 전공정 또한 미세화를 지속했다. 이를 지원하는 EDA 툴은 물론 미세화로 인해 발생한 예상치 못한 문제를 해결하는 EDA 툴도 필요해졌다. EDA 업계는 이때부터 단순히 파운드리 업체의 공정을 지원하는 개념을 넘어 파운드리 업체와 함께 EDA 툴을 개발하기 시작했다.

첨단 공정의 가장 큰 난제는 배선 저항의 증가다. 반도체는 금속 선을 통해 각 회로 블록(block)과 계층(Layer)에 전력을 공급하는데, 금속 선 두께가 얇아지면서 저항이 커진다. 배선 저항은 16나노에서 7나노로 오면서 3배 늘었고, 7나노에서 5나노로 올 때 또다시 3배가 됐다.

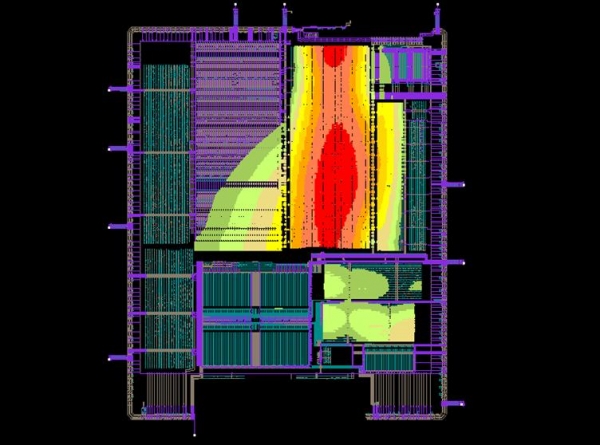

배선 저항이 커지면 에너지 손실로 인해 전압 강하(IR-drop) 현상이 발생해 각 셀(Cell)에 충분한 전압이 도달하지 못하는 문제가 발생한다. 이는 곧 전체 성능도 저하시키고 설계 당시 설정해놓은 것보다 시간이 더 걸려서야 칩이 작동하는 결과를 초래한다.

이 문제는 7나노 공정에서부터 수면 위로 떠올랐다. 초기 업계는 전압 강하 현상이 어떻게, 왜 발생하고 어떤 영향을 미치는지조차 가늠하지 못했다. 전압 강하 따로, 타이밍(Timing) 따로 분석하던 기존 EDA 툴의 접근법으로는 이를 감지할 수 없었기 때문이다.

케이던스는 파운드리 업계와 협업, 전체 회로 중에서도 유난히 전압 강하 현상에 대해 많은 영향을 받는 ‘IR 민감 경로(IR-Sensitive path)’가 있다는 걸 찾아냈다. 접근법을 바꿔 이를 설계 단계에서 분석, 반영할 수 있는 툴도 내놨다.

시윈스키 부사장은 “이전까지 EDA 업계는 각 공정을 ‘지원’하는 툴만 제공해왔지만, 이제는 설계부터 제조에 이르기까지 전체 흐름에 초점을 둬 툴을 개발해야한다”며 “5나노·3나노 등 첨단 노드는 단순히 공정이 아닌, 공정과 자동화 툴이 결합한 결과물”이라고 설명했다.

셋. 새로운 설계 환경을 제공하다

반도체 기술 발전과 함께 설계 비용 또한 급격히 증가하고 있다. EDA 툴 라이선스 비용도 마찬가지다. 중소기업들은 EDA 툴 라이선스 비용에 혀를 내두른다.

이처럼 설계 비용이 비싸지는 건 검증(Verification)과 소프트웨어(SW) 때문이다. 전체 프로젝트 비용의 70% 가량이 여기에 쓰인다. 시스템 수준에서는 분석이 더 중요하기 때문에 비용이 더 늘어난다.

업계는 먼저 자체 서버와 고성능 컴퓨터가 없는 기업도 EDA 툴을 쓸 수 있게 클라우드 환경을 지원하고 있다. 케이던스는 5년 전부터 클라우드 지원을 시작했고, 현재는 모든 툴에서 클라우드 환경을 지원한다.

그는 “우리가 최근 개발한 툴들은 프로젝트 비용을 줄이는 데 초점이 있다”며 “임베디드 SW 업체와 협력해 새로운 툴을 개발하고 있고, 소프트웨어 및 하드웨어의 유효성 검사에 대한 3D 분석 기능도 연구 중”이라고 말했다.

인공지능(AI)·자율주행 등 시스템적인 차원에서 접근해야하는 응용처를 위한 설계 환경도 조성하고 있다. 반도체에 익숙하지 않은 업체들이 자체 반도체 설계에 나서면서 EDA 업계는 이들도 반도체를 만들 수 있도록 지원을 아끼지 않고 있다. 케이던스는 인텔리전스 시스템 전략을 발표, 제품군을 반도체에서 시스템 및 소프트웨어로 넓혔다.

시윈스키 부사장은 “모든 시스템과 응용처는 기계학습(ML) 등의 기술을 통해 지능형(Intelligence)에 어떤 식으로든 의존하게 될 것”이라며 “모바일 등 전자 제품의 시대가 끝났다고 보는 의견도 있지만, 나는 이제 막 시작했다고 본다”고 말했다.