삼성전자⋅SK하이닉스도 3D 낸드에 하이브리드 본딩 전망

D램도 하이브리드 본딩으로 집적도 개선 가능

그동안 CIS(이미지센서)나 로직 반도체 솔루션으로 부각됐던 하이브리드 본딩 기술이 메모리 반도체 분야로 침투하고 있다. 3D 낸드플래시에 이어 D램에서도 집적도를 높이기 위한 기술로서 하이브리드 본딩 기술이 적용될 전망이다.

삼성전자⋅SK하이닉스도 3D 낸드에 하이브리드 본딩 전망

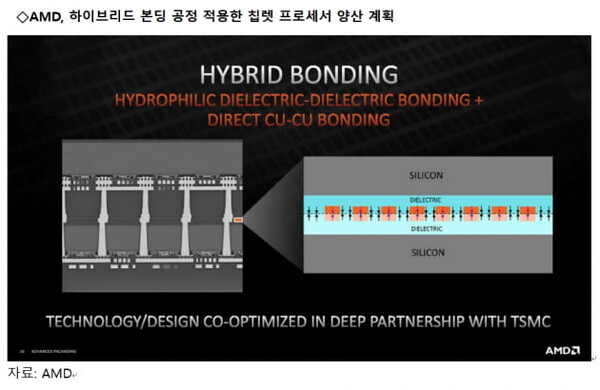

하이브리드 본딩은 두개의 칩을 이어 붙일때, 따로 범프를 형성하지 않고 계면과 계면을 바로 이어 붙이는 것을 뜻한다. 아래위 칩 간에 산화물 면과 구리 면 사이에 동시에 본딩이 일어난다는 뜻에서 하이브리드 본딩이라는 이름이 붙었다. 범프 없이 구리와 구리가 바로 붙는다는 점에서 ‘카파 투 카파(Copper to Copper)’ 본딩이라고도 부른다.

현재 반도체 업계서 하이브리드 본딩이 가장 화두로 떠오른 곳은 CPU 등 로직 반도체 분야다. 칩을 기능별로 쪼개어 생산(칩렛, Chiplet)한 뒤, 하이브리드 본딩으로 이어 붙이면서다. 이 같은 방식은 단일 반도체 다이 사이즈를 줄임으로써 웨이퍼 수율을 제고할 수 있게 해준다. 인텔의 차세대 CPU ‘메테오레이크'가 칩렛 방식 생산 기술을 활용해 생산된다.

이 같은 로직칩과 달리, 메모리 반도체는 셀을 쪼개는 게 무의미하기에 그 동안 하이브리드 본딩과는 거리를 뒀다. 그러나 중국 YMTC가 3D 낸드플래시 생산에 처음 하이브리드 본딩 기술을 쓴 이후 기존 플레이어들도 양산 적용을 검토하고 있다. 이미 일본 키옥시아는 과점 사업자로서는 처음 3D 낸드플래시 생산에 하이브리드 본딩 기술을 차용했다.

최정동 테크인사트 펠로우는 “키옥시아가 양산 제품에 처음 하이브리드 본딩 기술을 썼다"며 “삼성전자⋅SK하이닉스도 곧 같은 기술을 쓰게 될 것”이라고 말했다. 키옥시아는 200단 이전 제품까지는 주변부회로(Peri)와 셀을 한 장의 웨이퍼 위에서 생산하는 방식을 택했다. 이를 CUA(Circuit Under Array)라고 하는데, 삼성전자의 COP(Cell On Peri)도 이름만 다를 뿐 같은 방식이다.

그러나 키옥시아는 218단 제품부터는 주변부회로와 셀을 각각의 웨이퍼에서 생산한 뒤 하이브리드 본딩으로 이어 붙이는 방식을 택했다. 이를 CBA(CMOS Direct Bonded to Array)라고 명명했다. YMTC가 ‘엑스태킹'으로 부르는 기술과 동일한 방식이다.

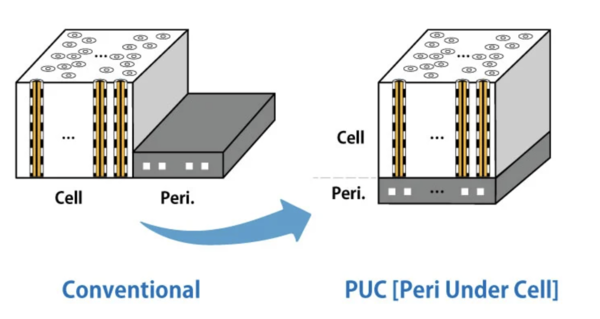

이처럼 주변부회로와 셀을 따로 생산하면 3D 낸드플래시 집적도를 높일 수 있다는 것은 익히 알려져왔지만, 대형 공급사들은 양산 적용을 최대한 미뤄왔다. 하이브리드 본딩을 위해서는 관련 공정을 따로 구축해야 하는데다, 낸드플래시 양산에 웨이퍼를 두 장씩 써야 하기 때문이다. 이에 삼성전자는 218단 제품에, SK하이닉스는 238단 제품에 여전히 COP 방식(SK하이닉스는 PUC)을 택했다.

다만 향후 300단 이상으로 3D 낸드플래시의 종횡비가 더 높아지면 더 이상 하이브리드 본딩 도입을 미룰 수 없을 것으로 본다. 한 반도체 산업 전문가는 “약 5년 뒤에는 키옥시아 뿐만 아니라 삼성전자⋅SK하이닉스 등 메이저 낸드플래시 회사 모두 하이브리드 본딩 기술을 쓰고 있을 것”으로 예상했다.

D램에도 하이브리드 본딩

이처럼 주변부회로를 따로 빼서 셀 집적도를 높일 수 있는 컨셉트는 낸드플래시 뿐만 아니라 D램에도 적용할 수 있다. D램에도 구동을 위한 주변부회로가 있는데, 현재는 D램 내부에 혼재돼 있다. 이 때문에 D램의 공간 활용도를 떨어뜨리는데, 주변부회로를 별도의 웨이퍼에 만들어 이어 붙이면 3D 낸드플래시처럼 집적도를 개선할 수 있다.

실제 중국 선룬(Sunlune)사가 개발한 이더리움 채굴용 ASIC(주문형반도체)은 40nm 디자인 로직칩과 27nm 디자인의 D램을 하이브리드 본딩으로 이어 붙인 제품이다. 최정동 펠로우는 “비록 이 ASIC에 붙은 D램이 레거시 제품이기는 하지만 D램과 로직칩을 하이브리드 본딩으로 이어 붙일 수 있다는 컨셉트는 검증된 사례”라고 설명했다.