SK하이닉스-마이크론, CTF로 구조 변경… 미래는 '멀티 스태킹'

▲SK하이닉스의 96단 낸드 제품군./SK하이닉스

낸드플래시 메모리 업계가 구조 혁신을 거듭하고 있다. 2차원(2D) 평면 구조에서 3D, 이제는 4D까지 나왔다.

삼성전자와 SK하이닉스, 마이크론, 도시바 4개사가 내놓은 초기 3D 낸드는 서로 구조가 달랐다. 하지만 층고가 높아지면서 이제 각 사의 낸드는 서로 비슷한 모습을 하고 있게 될 것으로 보인다.

2D에서 3D로… 삼성전자 혁신 주도

▲(왼쪽부터 시계방향)플로팅게이트 구조, 2D CTF 구조. 3D CTF 구조./삼성전자

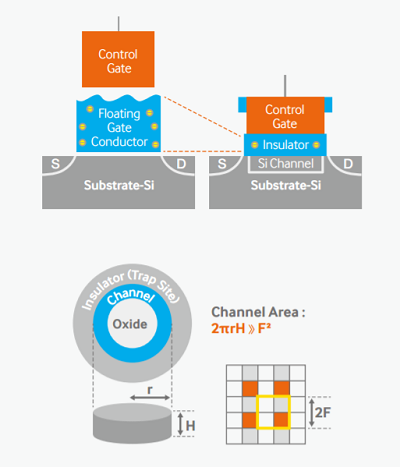

기존 2D 낸드는 도체인 플로팅게이트(Floating Gate)에 전하를 가두는 방식으로 데이터를 저장했다. 하지만 미세화로 플로팅 게이트가 점점 좁아지면서 전자가 누설돼 셀 간 간섭 현상(Cross talk)이 나타났다.

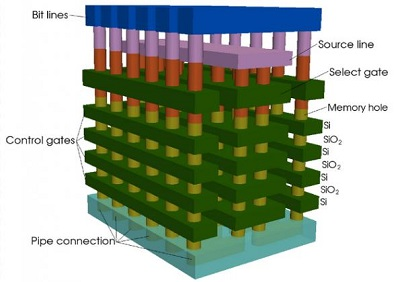

이에 삼성전자는 업계 처음으로 플로팅게이트 대신 부도체인 CTF와 컨트롤게이트를 층층이 쌓은 3D 낸드를 구현했다. 실리콘 질화물(SiN)과 실리카(SiO2)를 층층이 쌓아 CTF를 만들고, 구멍(hole)을 뚫어 전하를 채우고 비우는 방식으로 데이터를 저장, 삭제한다.

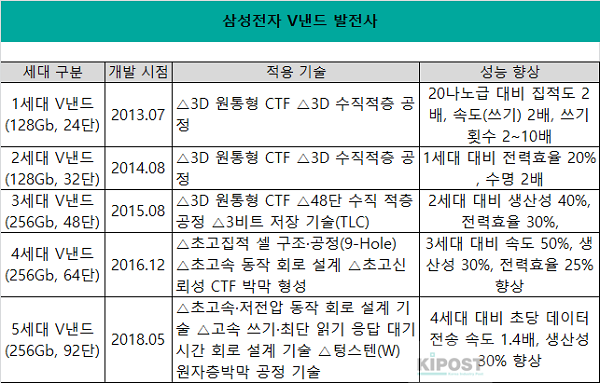

삼성전자는 이 구조를 기반으로 원자층증착(ALD) 기술을 활용, 층고를 낮추고 고속 회로 기술을 적용해가며 ‘V낸드’를 발전시켜왔다.

▲삼성전자의 V낸드 발전사./삼성전자, KIPOST 정리

지난 5월 개발 완료된 5세대 V낸드(92단)은 회로 설계 기술로 초고속·저전압 동작을 구현하면서 쓰기 속도를 높였고 읽기 응답 대기 시간은 줄였다. 컨트롤 게이트를 구성하는 텅스텐(W)을 ALD로 얇게 깔아 동작 오류를 줄이고 판독 범위를 확대했다.

SK하이닉스, 4D 낸드 개발… 연내 초도 양산 시작

SK하이닉스는 지난 달 말 96단 512Gb 트리플레벨셀(TLC) 낸드를 개발 완료하고, 연내 초도 양산을 시작한다. 초도 양산은 M14 2층에서, 양산은 M15에서 하게 된다.

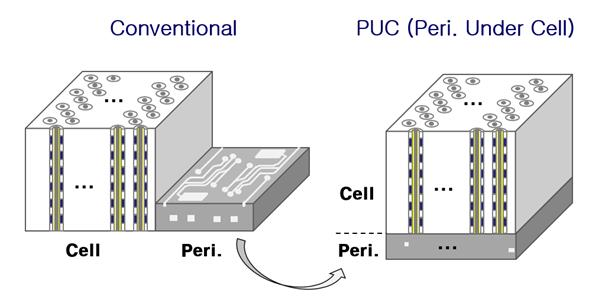

SK하이닉스의 96단 TLC 낸드는 차치트랩플래시(CTF)와 페리언더셀(PUC)을 결합한 4차원(4D) 구조다. 한 칩 하나에 총 64GB의 용량을 담을 수 있어 기존 256Gb 3D 낸드 2개를 완벽히 대체할 수 있다. 현재 개발 중인 128단 낸드도 96단 낸드와 같은 구조다.

3D CTF 구조에 셀 작동을 관장하는 주변부 회로를 CTF 아래에 배치하는 PUC 기술을 적용, 업계 최고 수준(Best in Class)의 성능과 생산성을 달성했다. 아파트 옆에 만들던 옥외 주차장을 지하 주차장으로 내려 공간 효율성을 확보한 셈이다.

▲SK하이닉스는 셀 옆에 붙어있던 주변회로(Peri)를 셀 아래로 배치해 공간 효율성을 확보했다./SK하이닉스

이를 통해 72단 512Gb 3D 낸드보다 칩 사이즈는 30% 이상 줄었고, 웨이퍼 당 생산할 수 있는 칩의 개수가 50% 늘었다. 쓰기, 읽기 성능은 72단 제품보다 30%, 25% 높아졌다.

또 칩 내부에 플레인(Plane)을 4개 배치, 데이터 대역폭을 32KB에서 64KB로 2배 늘렸다. 다중 게이트 절연막 구조와 새로운 설계 기술을 도입, 입출력(I/O) 당 전송 속도는 1200Mbps까지 높이고 동작전압은 1.2V로 낮춰 전력 효율도 72단 대비 150% 개선했다.

SK하이닉스는 96단 512Gb 4D 낸드에 자체 개발 컨트롤러와 펌웨어를 탑재한 최대 1TB 용량의 소비자용(Client) 솔리드스테이트드라이브(SSD)를 연내 선보인다.

휴렛팩커드(HP), 마이크로소프트(MS) 등 고객사의 인증을 마치고 사업을 본격화하고 있는 72단 기반 기업용 SSD도 내년 96단으로 전환, 경쟁력을 강화할 계획이다.

차세대 스마트폰에 채용될 예정인 유니버셜플래시스토리지(UFS) 3.0도 96단 낸드에 자체 컨트롤러, 펌웨어를 탑재해 내년 상반기 내놔 모바일 솔루션 시장도 공략한다. 내년 중 96단 4D 낸드 기반 1Tb TLC와 1Tb 쿼드레벨셀(QLC) 제품도 출시 예정이다.

플로팅게이트 고집하던 마이크론, 4세대부터 CTF 적용

마이크론은 인텔과 함께 3세대(96단) 3D 낸드(단)까지 플로팅게이트 방식을 고집해왔다. CTF는 셀 구조가 간단해 만들기 쉽고 그만큼 제조 비용을 아낄 수 있지만 고온 특성 등 수명은 CTF 방식보다 플로팅게이트가 유리하다는 이유를 들었다.

▲마이크론 3D 낸드 단면(왼쪽)과 탑뷰(오른쪽). 주변부 회로를 메모리 아래 배치하는 ‘CuA’ 기술이 적용됐다./마이크론

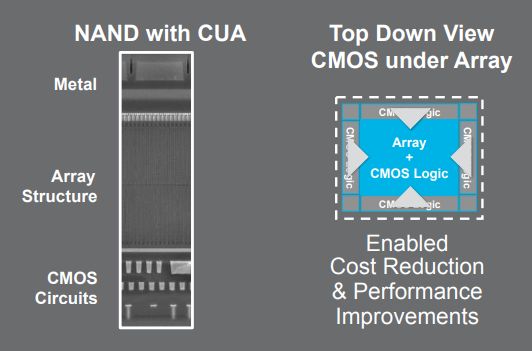

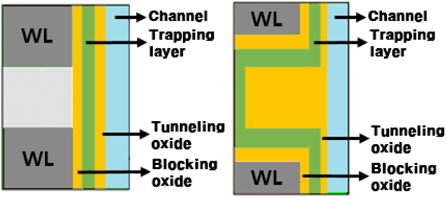

마이크론과 인텔 진영은 플로팅게이트와 컨트롤게이트를 원통형으로 만들고, 메모리 아래 주변 회로를 배치했다. PUC 기술을 플로팅게이트에 접목한 셈이다. 마이크론에서는 이를 ‘CMOS 언더 어레이(CuA·CMOS under array)’라고 부른다.

인텔과 결별한 후 마이크론도 4세대 낸드(128단 예상)부터 CTF 방식을 적용하기로 했다. 신뢰성을 희생하더라도 CTF 방식으로 제조 비용을 낮추겠다는 전략이다.

지난 8월 개최된 ‘플래시메모리서밋(FMS) 2018’에서 러스 메이어(Russ Meyer) 마이크론 부사장은 “4세대 낸드부터 ‘charge trap cell’ 기술을 사용할 것”이라며 “이를 통해 4세대 낸드의 대역폭은 96단 낸드보다 30% 향상되고 전력소모량은 40% 줄어들 것”이라고 설명했다.

만들고 접는다… 도시바의 ‘P-BiCS’ 기술

▲도시바와 샌디스크 연합의 BiCS 구조./도시바

도시바는 ‘파이프 모양의 비트 코스트 스케일링(P-BiCS)’이라고 부르는 3D 낸드 기술을 활용했다.

삼성전자처럼 CTF 방식이지만, 차이점이 있다.

▲도시바의 BiCS 구조(왼쪽)와 삼성전자의 TCAT 구조./OAK

삼성전자는 홈을 파서 타노스(TANOS·Ta/AIO/Nitride/Oxide/Si) 셀을 증착한 뒤 가장 마지막 공정에서 질화물 자리에 금속 게이트를 만들었다면(Gate last), 도시바는 ‘소노스(SONOS·Si/Oxide/Nitride/Oxide/Si)’ 셀을 올려 게이트를 먼저(Gate first) 구현했다.

채널 소재로 실리카 대신 폴리실리콘을 쓴다는 점도 다르다.

여기에 32단 낸드를 2개 형성해 접어서 64단을 만들고, 같은 방식을 적용해 48단 2개로 96단을 만드는 ‘멀티 스태킹(Multi-stacking)’ 기술을 적용했다. 2개의 셀 스트링을 1개의 파이프로 연결해 ‘P’라는 이름이 붙었다.

삼성전자처럼 단일 스택에서 적층 단수를 높여가는 것보다는 생산성이 떨어지지만 만들기는 쉽다. 또 속도와 크기에서 뒤지지만 확장성과 신뢰성이 높다는 게 도시바의 설명이다.

미래 V낸드 구조는?

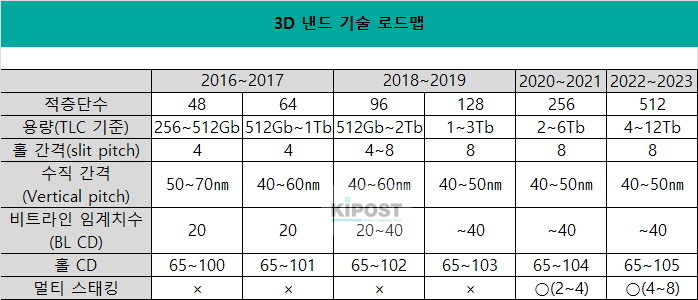

미래의 V낸드 구조는 어떤 모양일까. 일단 낸드 4개사가 모두 CTF 구조로 가닥을 잡았다. 주변 회로의 위치도 서로 다르지만 더 눈여겨 봐야하는 것은 적층 방식이다.

제일 먼저 발전해야하는 건 증착과 식각 기술이다. 96단 낸드의 종횡비(A/R)는 1:70 이상이다. 집에서 쓰는 바늘의 종횡비(1:47.5)보다 훨씬 얇고 길게 구멍을 뚫어 채널을 만들어야한다.

현재는 이온의 반응으로 식각이 진행되는 반응성 이온식각(RIE) 기술이 활용되지만 오래 걸리고 수율이 낮다. 더욱이 층고가 높아지면 셀 아래로 내려갈수록 이온의 수가 줄어들고 식각 속도가 떨어져 균일성을 확보하기 어렵다.

불소계 고밀도 플라즈마를 활용한 극저온 식각 기술을 활용하면 상대적으로 스트레스가 적고 균일도를 확보할 수 있지만 처리량(Throughput)이 급격히 감소할 뿐더러 난이도도, 비용도 증가한다.

증착도 문제다. 수백개의 층을 정확한 두께로 균일하게 쌓아올리기는 쉽지 않다. ALD로 할 수는 있지만 역시 처리량이 발목을 잡고 있고, 증착 과정에서 스트레스를 받아 층이 구부러지거나 하는 결함이 발생할 가능성이 크다. 업계가 ALD 사용을 최소화하는 이유다.

때문에 학계에서는 삼성전자처럼 단일 영역에서 층고를 쌓아올리는 ‘싱글 덱 스택(Single Deck Stack)’으로는 층고를 높이는 데 한계가 있을 것이라고 본다. 현재의 식각 기술로는 한 번에 128단을 파낼 수 있지만 균일성이 떨어지고 주변 셀에 스트레스를 준다.

▲3D 낸드 기술 로드맵./Imec, KIPOST 재구성

때문에 그 이상부터는 멀티 스태킹 기술을 활용할 가능성이 높다. 2개 이상의 덱(Deck)을 쌓아 올리는 방식이기 때문에 이전보다 생산량은 줄어들고 공정 단계(step)와 시간이 늘어나는 것은 불가피하다. 하지만 수율 확보는 상대적으로 용이하다.

식각 장비 업체 관계자는 “단일 스태킹 기술을 활용하는 업체들은 128단에서 256단으로 바로 점프업하는 것보다 100단 후반대의 중간 노드를 선택해 속도를 늦추는 식으로 멀티 스태킹 기술을 적용할지의 여부를 결정할 것”이라고 설명했다.