D램·로직에 이어 3D 낸드까지… '선택적 ALD'도 각광

반도체 공정에서 ‘원자층증착(ALD)’ 쓰임새가 늘고 있다.

전자의 흐름을 제어하는 절연층 증착에 활용되기 시작한 이 기술은 최근 금속 배선 공정까지 적용 범위를 넓혔다.

단점인 처리량(Throughput) 개선은 물론, 현재의 반도체 제조 공정을 완전히 뒤바꿀 수 있는 ‘영역 선택적(Area Selective) ALD’에 대한 연구개발(R&D)도 한창이다.

ALD, 화학 증착부터 금속 증착까지

▲반도체 단면도. 반도체는 수십 가지의 층으로 이뤄져있다./삼성반도체이야기

반도체는 수십 가지의 층(layer)으로 구성돼있다. 각 층은 노광으로 패턴을 그린 후 원하는 소재를 층층이 쌓고 불필요한 부분을 제거하는 과정을 반복해 만든다.

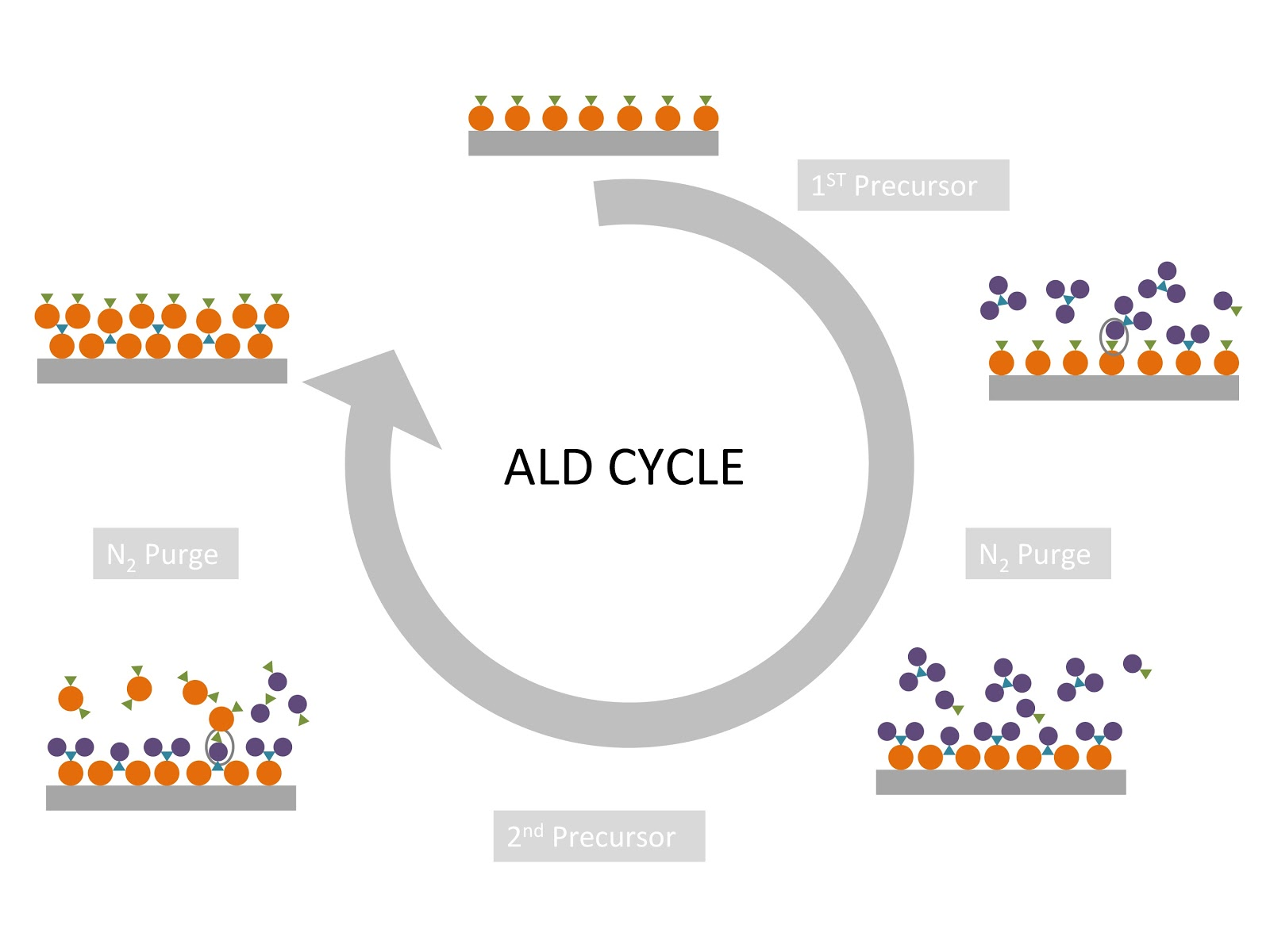

▲ALD 공정은 특정 소재를 1차로 깐 뒤 이에 반응하는 물질을 도포, 화학적 반응을 이용해 소재를 ‘성장(Growth)’시키는 과정을 수십번 반복한다./Ctechnano

ALD는 저온에서 소재와 소재의 화학 반응을 이용, 표면에 원자층을 층층이 ‘성장(Growth)’하는 증착 기술로 금속이든 비금속이든 적용 가능하다. 박막 두께를 수 옹스트롬(Å=0.1㎚) 단위로 조절할 수 있고 단차피복성(step coverage·높이가 서로 다른 부분에 소재를 균일하게 증착하는 특성)이 우수하다.

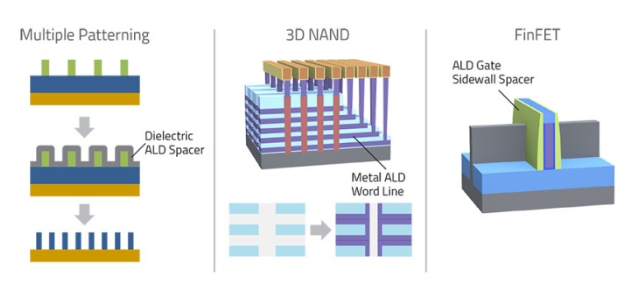

▲ALD 기술은 D램 유전막 형성에 이어 패터닝과 3D 낸드, FinFET 등 다양한 분야에서 활용되고 있다. 다중 패터닝 공정에서는 원하는 패턴을 보호하는 실리콘 옥사이드 층을 만들고, 3D 낸드에서는 워드라인(Word Line)에 텅스텐을 채울 때 활용된다./램리서치

처음 ALD가 도입된 건 D램 캐패시터(Capacitor)의 절연막이다. 회로 선폭이 90나노(㎚) 아래로 줄어들면서 전하를 저장하는 캐패시터의 가로 대 세로 비율(A/R)이 높아졌고, 기존 화학기상증착(CVD)으로는 내부 절연막의 균일성을 확보할 수 없었다.

로직(Logic) 반도체에서는 인텔이 첫 발을 끊었다. 인텔은 45나노 공정에서부터 게이트 내부에 있는 전하가 절연층을 뚫고 나가는 누설 전류 문제를 막기 위해 고유전율(High-k) 소재의 게이트 절연층을 ALD로 만들었다.

이렇게 얇은 절연층을 주로 만들던 ALD는 금속 증착으로까지 범위를 넓히고 있다. 특히 64단 이상 고층 3D 낸드에서 전자가 오가는 워드 라인(Word line)을 금속으로 채울 때도 ALD가 활용된다.

이전에는 대부분 육불화화합물(WF6) 가스와 수소(H2) 가스를 한 번에 주입해 CVD로 텅스텐 층을 만들었다. 하지만 층수가 높아지면서 남은 불소(F)로 인한 결함(Defect)이 야기 됐고, 3D 구조물의 각 위치마다 금속 층의 두께가 달라지는 문제가 발생했다. ALD로 얇고 균일한 층을 만들면 이를 해결할 수 있다.

최근에는 티타늄(Ti)이나 탄탈륨(Ta) 등의 게이트 전극도 ALD로 형성하는 것을 검토 중이다. 종횡비가 높아지면 게이트 절연층이 받는 스트레스가 커진다. 기존 CVD로는 게이트 층을 얇게 만들면서 동시에 밀도를 높이는 데 한계가 있어서다.

처리량 개선 작업 박차

ALD 기술의 가장 큰 문제는 처리량이다. 흡착과 화학 반응을 이용하다보니 하나의 층을 형성할 때 오랜 시간이 걸린다.

한 기기 안에 여러 장, 최대 4장의 웨이퍼를 넣는 세미-배치(semi batch) 타입 장비가 나왔지만, 시간당 웨이퍼 처리량이 플라즈마 화학기상증착(PE-CVD)의 수십분의 1에 불과하다.

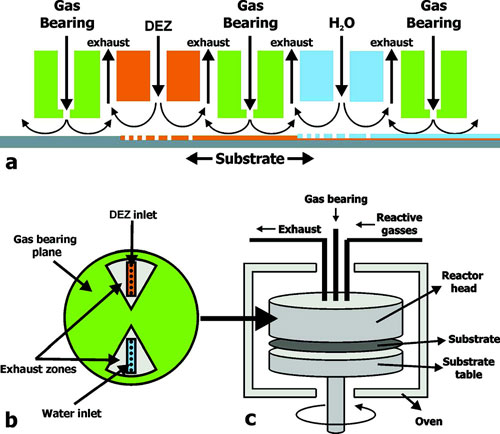

▲a는 ‘Temporal ALD’, b는 ‘공간적(Spatial) ALD’ 모식도./internano

업계에서는 웨이퍼를 이동해 각기 다른 전구체에 노출될 수 있게 하는 ‘시간적(Temporal) ALD’, 웨이퍼를 고정시키고, 돌려가면서 필요한 전구체를 챔버 안에 삽입·제거하는 ‘공간적(Spatial) ALD’를 고안하고 있다.

이처럼 장비 콘셉트가 나오자 진공관이나 챔버의 환경을 맞춤화하고, 소재 특성을 최적화하기 위한 대한 연구가 뒤따르고 있다.

반도체 패러다임 바꾸는 ‘영역 선택적 ALD’

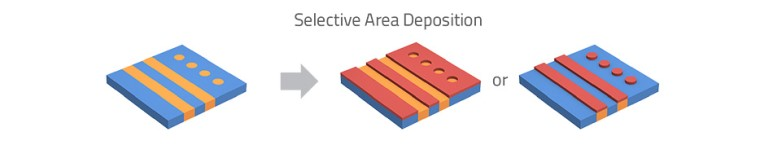

▲영역 선택적 ALD는 패턴을 그린 후 원하는 영역에만 층을 형성하는 기술이다./램리서치

반도체 공정의 패러다임을 바꿀 수 있는 ‘영역 선택적 ALD’도 각광받고 있다. ‘영역 선택적 ALD’는 원하는 구역에만 절연막이나 금속막이 깔려 그 자체로 하나의 레이어를 만드는 바텀업(bottom-up) 방식의 증착 기술이다.

노광 후 식각과 증착, 평탄화(CMP) 공정을 거치는 지금과 달리 증착 한번으로 층을 형성하기 때문에 반도체 제조 공정을 대폭 줄일 수 있다. 반도체 구조가 복잡해지면서 생긴 층 간 정렬(alignment) 문제나 균일성 문제에서도 자유롭다.

램리서치, 도쿄일렉트론(TEL) 등 글로벌 장비 업체들은 소재 업체들과 함께 ‘영역 선택적 ALD’로 모노레이어(monolayer)를 만들고 ‘원자층 식각(ALE)’ 기술로 표면에 남은 원자 단위의 이물질을 없애는 기술을 집중 개발하고 있다.

전문가들은 이 기술이 차세대 금속 소재로 꼽히는 루테늄(Ru) 층을 만들때 활용될 것이라 내다본다.

루테늄은 7나노 이하 반도체 제조 공정에서 구리 배선의 촉매(Seed) 층으로 연구개발이 한창인 소재로, 차세대 D램 캐패시터 전극으로도 각광받고 있다. 희귀 금속이라 가격이 비싸다는 게 흠이다.

전형탁 한양대 교수는 “ALD는 균일성(Uniformity), 결함(Defect)에서 다른 증착 기술보다 유리하다”며 “회로 선폭이 좁아질수록, 3D 반도체의 층고가 높아질수록 ALD의 역할은 커질 것다”고 말했다.