본격 양산은 2025년 2nm 제품으로 전망

대만 TSMC가 오는 2024년 고개구수(High NA, 하이 NA) EUV(극자외선) 노광장비를 도입한다고 IT즈자가 16일 보도했다. 하이 NA EUV 장비는 네덜란드 ASML이 생산하는 EUV 설비 중 광학부품의 해상력을 높인 제품이다. 현재 TSMC를 비롯해 글로벌 파운드리 업체들이 도입하는 EUV 설비로는 3nm(나노미터) 안팎 제품까지 생산할 수 있으나 2nm, 혹은 옹스트롱 단위 미세공정까지 구현하려면 하이 NA 노광장비가 필수다.

하이NA EUV 노광장비는 한 대 가격이 4억달러(약 5600억원) 정도로, 기존 EUV 장비 대비 2~3배 비싸다. 그러나 TSMC⋅삼성전자⋅인텔 등이 앞다퉈 도입하고 있다. 올해 초 인텔은 1.8nm 공정 제품 생산을 위해 오는 2025년 5대의 하이 NA EUV 설비를 구매하기로 계약을 체결한 바 있다. 삼성전자 역시 이재용 부회장이 직접 네덜란드 ASML 본사를 방문, 하이 NA 장비 도입을 타진했다.

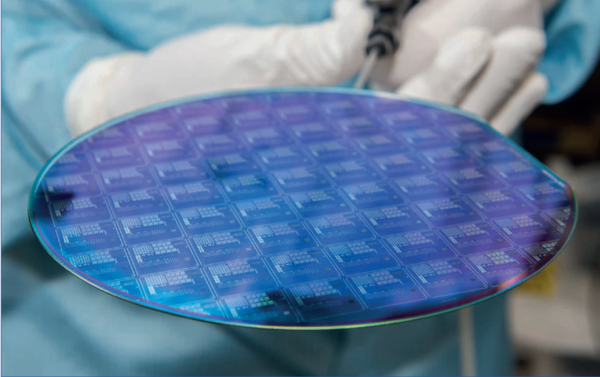

TSMC는 2025년부터 2nm 공정 양산을 시작할 계획인데, 여기에 하이 NA EUV 설비가 사용될 것으로 예상된다. TSMC 2nm 제품은 기존 3nm의 핀펫 구조와 달리 게이트올어라운드(GAA) 구조가 채택된다. GAA는 전자 흐름을 제어하는 게이트가 채널을 4면에서 감싸는 구조다. 삼성전자는 이를 3nm 제품부터 적용했다.

IT즈자는 “TSMC가 하이 NA EUV를 이용한 리스크 생산을 2024년 시작해 본격 양산은 2025년 돌입할 예정”이라며 “칩이 고객사에 인도되는 시점은 2025년으로 예상된다”고 말했다.