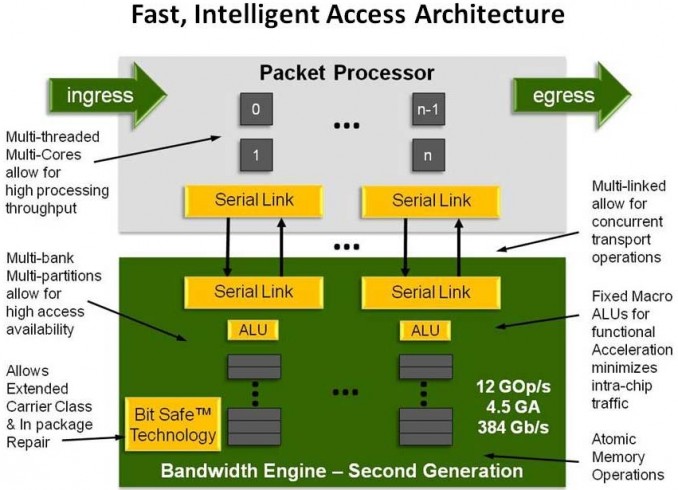

(iTers News) - MoSys, a leader in semiconductor solutions that enable fast, intelligent data access for network and communications systems, today announced sample availability of its Bandwidth Engine 2 - Access device, delivering random access performance with more than four times the capacity and more than twice the access performance of any SRAM on the market today. The device is based on an architecture of four 144 Megabit (Mbit) partitions, each running at 375MHz with true dual-port, random access capability. The partitions are addressed as a single-bank to enable a dramatic increase in processing rate capability.

The Bandwidth Engine family of ICs is optimized for high-performance networking equipment requiring aggregate bandwidth of 40G, 100G, 400G or higher, bringing fast, intelligent memory access to packet and data processing applications. Any application requiring true random access using traditional SRAM devices is limited to densities of 144 Mbits. The MoSys MSR720 breaks through this barrier by delivering 576 Mbit capacity and up to 4.5 billion accesses per second, at least twice the access rate of a traditional SRAM. The dual-ported partitions rely on address compare and data bypass to ensure fully coherent data under any access condition. With its ability to simultaneously read and write to a specific memory location, the MSR720 delivers substantial performance and efficiency advantages over the alternatives.

The unique device architecture and serial interface of the MSR720 maintains full data coherency, high command efficiency and simplified scheduling, resulting in a performance of up to 4.5 GigaAccesses per second. The high access rates and reduced effective cycle time of the MSR720 are well-suited to the requirements of state memory and queuing applications, where repeat access of the same address is needed.

"Our second generation Bandwidth Engine architecture supports purpose-built variants to optimize specific applications and access types," stated John Monson, Vice President of Marketing for MoSys. "The MSR720 is intended to integrate the random access capabilities of traditional SRAM and relieve constraints in capacity and performance, together dramatically reducing board area, power, economics and pin count."

The Bandwidth Engine family of ICs is designed, built and qualified for high-reliability, carrier-grade applications and utilizes a high-performance SerDes-based GigaChip Interface which has proven, robust compatibility with ASICs and FPGAs from Altera and Xilinx. The MSR720 is a member of the second generation family of Bandwidth Engine devices, which also includes the MSR620 device optimized for buffer applications and the MSR820 device with integrated macro functions to support on-chip functions, such as statistics and metering. MoSys is now accepting sample and preproduction orders for the MSR720, MSR620 and MSR820 devices.