소형화 및 전자파잡음(EMI)에 강해… 무선통신(RF)·3D 반도체에 활용도 높아

TSMC가 3년째 애플 애플리케이션프로세서(AP) 생산 물량을 싹쓸이하면서 반도체 후공정(OSAT) 업체들도 TSMC 따라잡기에 나섰다.

▲애플의 아이폰7 시리즈에 탑재된 'A10'은 TSMC가 생산했다. 이 칩에는 4개의 집적수동소자가 적용됐다./위키피디아

대표적인 게 팬아웃웨이퍼레벨패키지(Fo-WLP)에 수동소자를 내장하는 ‘집적수동소자(IPD·Intergrated passive devices)’ 기술이다.

비싼 가격 때문에 IPD를 외면했던 OSAT 업계도 연구개발(R&D)을 시작했다.

IPD, 웨이퍼레벨패키지와 만나다

IPD는 반도체 기판을 기반으로 만든 수동 소자다.

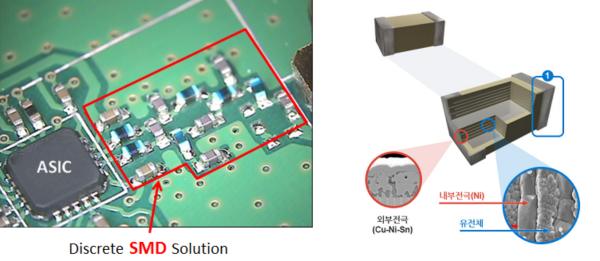

전자기기 메인보드 내 좁쌀처럼 생긴 부품이 수동소자다. 공급된 전력을 소비·축적·방출하는 역할을 한다.

AP나 메모리, 무선통신(RF) 반도체 같은 능동소자가 작동하기 위해서는 수십 개의 수동소자가 필요한데 소재가 세라믹이나 탄탈륨이라 실리콘을 쓰는 반도체와 물성이 달라 인쇄회로기판(PCB)에 별도로 실장해왔다.

▲전자기기의 메인 모드를 살펴보면 왼쪽 사진처럼 반도체 주변에 좁쌀만한 수동소자 여러 개가 있다. 오른쪽은 수동소자 중 하나인 적층세라믹콘덴서(MLCC)의 구조다./위키피디아 및 삼성전기

IPD는 이런 한계를 넘고자 수동소자 자체를 실리콘(Si)이나 유리, 갈륨비소(GaAs) 등 웨이퍼로 구현한 것이다. 능동소자와 하나로 패키지할 수 있기 때문에 보드 면적을 줄일 수 있고 전자가 이동하는 경로도 짧아져 전자파잡음(EMI) 및 정전기 방전(ESD) 성능도 좋아진다.

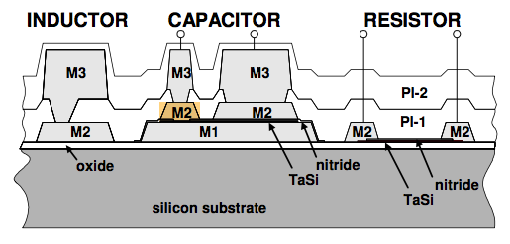

▲OSAT 업계는 웨이퍼 위에 수동소자들을 만들고, 후공정 시 반도체와 함께 몰딩(Molding)하는 서비스를 제공하고 있다. 보통 하나의 IPD 안에는 13~14개의 소자가 집적돼있다./STATSChipPAC

TSMC, TSV로 수동소자 실장

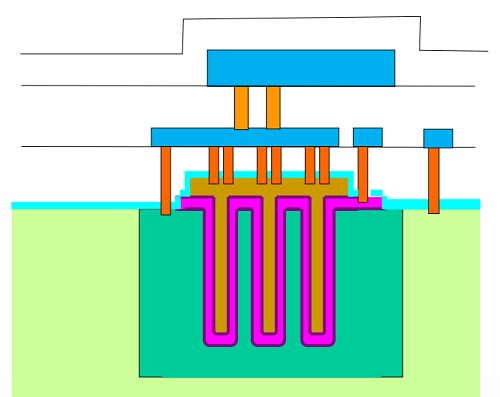

TSMC는 실리콘관통전극(TSV) 기술로 웨이퍼에 구멍(Hole)을 뚫고 유전체와 전극 소재를 적층해 커패시터를 만들었다. 일명 ‘딥 트렌치 커패시터(DTC·Deep Trench Capacitor)’다.

▲실리콘 기반 고밀도 딥 트렌치 커패시터 단면. 딥 트렌치 커패시터를 구현할 수 있는 곳은 TSMC와 무라타가 인수한 아이피디아(IPDiA) 정도다. 온세미컨덕터, ST마이크로 등 반도체 업체와 OSAT 업계는 아직 박막 IPD를 만든다./TSMC

커패시터에 저장하는 전력의 용량은 전하를 저장하는 소재의 양이 많을 수록 증가한다. 딥 트렌치 커패시터는 웨이퍼 내에서 표면적을 극대화할 수 있는 기술이다.

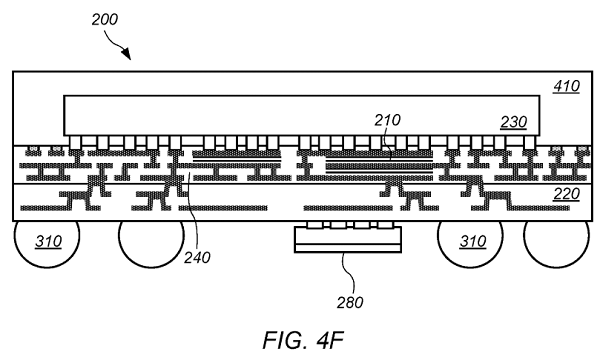

▲애플은 지난 2016년 미국 특허청으로부터 MIM 커패시터가 형성된 웨이퍼에 시스템반도체(SoC)를 배치하는 특허를 출원했다./미국 특허청

TSMC는 100㎛ 두께 정도의 작은 딥 트렌치 커패시터 4개를 AP 아래에 붙였다. 위 그림에서 280, 210이 커패시터다.

이 커패시터는 적층세라믹콘덴서(MLCC) 대신 ‘LSC(Land side capacitor)’ 역할로 쓰였다. MLCC를 썼을 때보다 온도, 주파수, 전자파 등의 문제를 개선했다고 TSMC는 밝혔다.

IPD 미래, 무선통신(RF)·3D 반도체

아직 IPD가 기존 수동소자를 완전히 대체할 수 있는 성능은 아니지만 OSAT 업계를 중심으로 연구개발이 활발히 진행 중이다.

업계가 6인치 생산 설비를 8인치로 전환하면서 생산량이 증가하고 있고, MLCC 등 기존 수동소자 가격이 치솟으면서 단가 차이도 좁혀지고 있다.

특히 무선통신(RF) 시장에서 이 기술에 대한 수요가 크다. RF 프론트엔드(RFFE) 부품의 상당수가 수동소자인데, 각 주파수 대역별로 수동소자가 여러 개 들어가야 해 소형화하기 어렵기 때문이다.

Fo-WLP 기반 2.5D 및 3D 반도체에도 활용도가 높다. 3D 반도체는 메모리와 로직(Logic) 반도체 등 서로 역할이 다른 반도체 소자들을 적층해 하나로 패키징한다. 2.5D 반도체는 실리콘 인터포저 위에 서로 다른 칩을 나란히 놓고 패키지하는 기술이다.

김준철 전자부품연구원 ICT디바이스·패키징연구센터 센터장은 “반도체와 적층할 수 없는 유일한 것이 수동소자”라며 “IPD의 장점인 소형화가 팬아웃 기반 시스템인패키지(SiP) 기술과 딱 맞아떨어진다”고 말했다.