D램·낸드·프로세서까지… '김기남 프로젝트'는 곳곳에서 문제

삼성전자가 2.5D 반도체를 양산한다. 소량이지만 두 곳의 고객사를 확보했다.

초기 수율 안정화에 초점을 맞추고 시장 수요를 감안해 생산량을 늘릴 계획이다.

TSMC에 빼앗긴 고성능 반도체 물량을 되찾아 올 수 있을지 주목된다.

고성능 프로세서 시장 겨냥하는 2.5D 반도체 기술

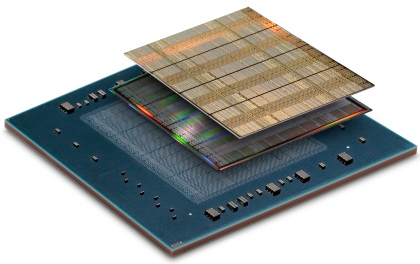

▲2.5D 반도체는 인터포저에 메모리 반도체와 로직(Logic) 반도체를 나란히 두고 실리콘관통전극(TSV) 기술로 연결한다./AMD

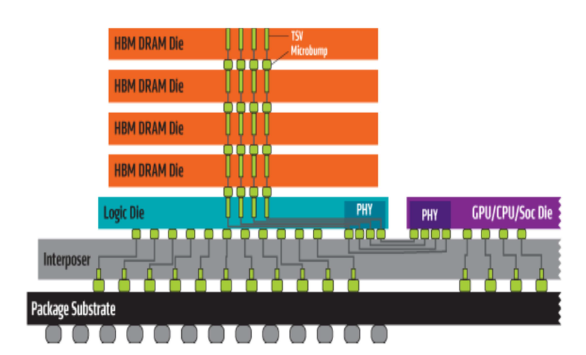

2.5D 반도체는 실리콘 인터포저(Silicon Interposer) 기판에 층층이 쌓은 메모리와 로직(Logic) 반도체를 실리콘관통전극(TSV) 기술로 연결, 패키징해 만든다. 메모리만 적층했다는 뜻에서 2.5D 반도체라는 이름이 붙었다.

TSV는 칩 자체에 수많은 구멍을 뚫고 배선 물질을 채워 넣어 칩과 칩 사이나 칩과 기판 사이를 연결하는 기술이다. AP와 메모리를 별도로 패키징할 때보다 칩 간 간격이 줄어들고, 수백~수천개의 구멍이 데이터 전송 통로 역할을 하기 때문에 고속·광대역 신호를 전송할 수 있다.

가격이 비싸다는 게 흠이지만 고성능 프로세서에 대한 수요가 커지면서 이를 상쇄하고 있다. 수율도 개선됐다. 양산 초기 20% 수준이던 수율은 현재 HBM2 TSV 기준 70~80%에 달한다.

삼성전자에 2.5D 반도체를 주문한 업체는 엔비디아와 샤오미로, 각각 자율주행용 프로세서와 인공지능(AI) 프로세서를 발주했다. 물량은 월 50만개다. 고대역폭메모리(HBM)과 애플리케이션프로세서(AP), 여기에 낸드 플래시메모리까지 담긴다. D램은 4개, 낸드는 2개, AP는 1개 탑재된다.

업계 전문가는 “수율이 높아지면서 이전보다 생산 단가도 많이 떨어졌다”며 “아직 전체 수율이 안정화된 상태는 아니기 때문에 초기에는 이를 끌어올리는 데 집중할 것으로 보인다”고 말했다.

2.5D 반도체 양산… ‘김기남 프로젝트’는 어디로?

당초 삼성전자가 올해 양산하기로 했던 기술은 2.5D 반도체가 아닌 3D 반도체였다.

3D 반도체는 로직 반도체와 메모리를 수직으로 쌓고 TSV로 연결한다. 성능을 개선하는 것은 물론 실리콘 인터포저 등에 들어가는 비용도 줄일 수 있다. 지난해 김기남 삼성전자 DS 부문 사장이 지시, 일명 ‘김기남 프로젝트’라고 불렸다.

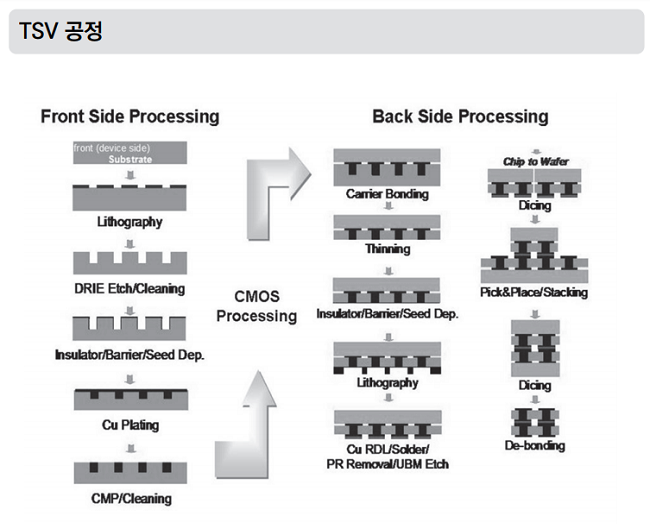

▲실리콘관통전극(TSV)의 공정 개념도. 삼성전자는 전공정(Front Side Processing)에서 트랜지스터를 형성한 후 TSV를 진행하는 ‘비아 미들(via middle)’ 방식을 채택하고 있다. /EVGroup

하지만 곳곳에서 난제가 등장했다.

삼성전자는 보쉬 DRIE(Deep reactive ion etching) 방식으로 웨이퍼에 구멍(via)을 형성한다. 보호막 증착과 식각을 반복하면서 차츰 차츰 구멍을 파내는 방식이다.

종횡비(A/R)가 높은 구멍을 한 번에 많이 뚫을 때 유리하지만, 구멍 내 표면이 우둘투둘해 배리어 층(Barrier layer)이 균일하게 증착되지 않는다.

배리어 층은 배선 소재인 구리(Cu)가 유전체 안으로 확산되는 것을 방지한다. 이 층의 두께가 일정하지 않으면 도금(plating) 시 구리가 배리어 층의 얇은 부분을 뚫고 유전체 안으로 들어가버린다.

삼성전자 TSV용 식각 장비를 공급하는 램리서치가 개선된 장비를 출시, 식각 균일성은 확보했으나 아직 증착 시 처리량(Throughput)은 개선이 더디다. 로직 반도체는 HBM보다 구멍이 많아 수율도 낮다.

이에 정통한 업계 관계자는 “전공정에서는 나노 단위로 얇게 구멍을 팠지만, TSV용 구멍은 수십 마이크로에 달한다”며 “크고 깊은 구멍에 소재를 같은 두께로 증착하려다 보니 처리량을 끌어올리는 데 한계가 있다”고 설명했다.

또 하나의 문제는 웨이퍼를 얇게 갈아낸(grinding) 후 휘어짐을 방지하기 위해 임시 부착하는 캐리어(carrier)를 떼내는 디본딩(De-bonding)에서 발생했다. 초기 빠르게 캐리어를 제거할 수 있는 레이저를 활용했지만 웨이퍼에 손상을 입히면서 수율이 떨어졌다. 이에 삼성전자는 자외선(UV) 경화로 방식을 바꿨다.

로직 반도체와 메모리 반도체의 성능이 다르다는 점도 발목을 잡았다.

고성능 프로세서는 발열량이 많다. D램은 85℃ 이상의 열이 가해지면 누설 전류가 증가, 데이터가 증발된다. 두 칩을 별도로 탑재할 때는 에폭시몰딩컴파운드(EMC)나 냉각 팬 등으로 시스템에 문제가 생기는 것을 줄일 수 있었다.

두 칩이 한 패키지 안에, 그것도 위 아래로 적층되면 공기가 잘 통하지 않아 방열 특성이 급격히 떨어진다.

HBM에서는 D램 사이 열을 빼내는 더미 범프를 넣거나 온도에 따라 초기화(Refresh) 주기를 구획(Bank) 별로 바꿔주는 기술로 이를 해결했지만, 칩 간 거리를 최대한 줄여 성능을 극대화하는 게 목적인 3D 반도체에는 적합하지 않다. 2.5D 반도체는 3D 반도체보다 칩 간 간격과 패키지 표면적이 넓어 이보다 방열에 강하다.

삼성전자 TSV라인에 장비를 납품한 한 업체 관계자는 “105℃, 125℃까지 동작하는 자동차용 D램 개발에 성공하자 자신감이 붙었고, 개발부터 구매부서까지 온통 3D 반도체에 매달렸지만 결국 양산 계획이 미뤄진 것으로 안다”며 “채산성도 맞지 않아 당분간은 2.5D 반도체 양산에 집중할 계획”이라고 말했다.