PDK 개발 등 초기 R&D용

TSMC에 뒤쳐진 선단공정 만회할까

삼성전자 파운드리 사업부가 3나노미터(nm) 공정 초기 연구개발(R&D)용 웨이퍼 투입을 시작했다. 팹리스 고객사들이 사용할 공정설계키트(PDK)를 개발하고, 초기 장비 세팅을 조율하기 위해서다.

삼성전자는 5nm 공정에서 양산 시기 및 물량⋅성능까지 대만 TSMC에 크게 뒤쳐졌다. 완전히 새로운 기술이 도입되는 3nm 경쟁에서는 파운드리 사업 전환점을 마련한다는 목표다.

6월부터 월 1000장 규모

삼성전자가 3nm 공정 R&D용 웨이퍼 투입을 시작한 건 지난 6월부터다. 매달 1000장 미만의 웨이퍼가 투입되고 있다. 5nm조차 지난 7월에서야 의미 있는 규모(약 3000장)의 웨이퍼 투입이 시작됐고, 4nm는 아직 양산 전이다. 따라서 3nm용으로 투입된 웨이퍼는 공정 개발 초기 단계의 R&D 용도다.

파운드리 업체는 고객사인 팹리스가 반도체를 설계할 수 있도록 PDK를 제공하는데, R&D 웨이퍼를 투입해보면서 PDK를 검증하고 업그레이드하는 것이다. 파운드리가 웨이퍼에 그림을 그리는 과정이라면 PDK는 붓과 팔레트 등의 도구다. 삼성전자는 이미 지난해 5월 3nm 1세대 초기버전용 PDK를 배포한 바 있다.

3nm 공정은 삼성전자 파운드리 사업에 전환점을 마련할 수 있는 계기다. 5nm까지 핀펫 기술로 TSMC와 경쟁해왔지만, 매번 수주 경쟁에서 밀렸다.

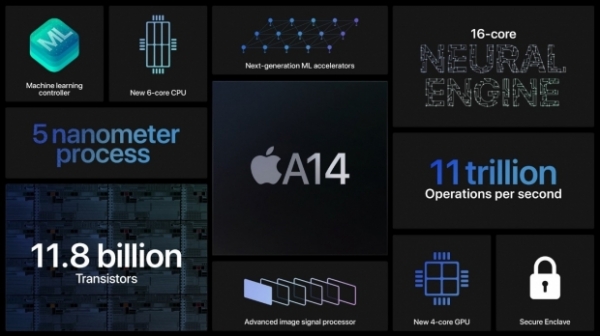

TSMC는 한 박자 빠른 선단 공정 양산과 높은 트랜지스터 밀도를 앞세워 애플⋅퀄컴 등 대형 고객사 애플리케이션프로세서(AP) 물량을 사실상 독점해왔다. TSMC는 지난 3분기 3564억3000만대만달러(약 13조8000억원)의 매출을 기록했는데, 5nm⋅7nm 매출 비중이 43%에 달했다. 5nm⋅7nm 공정만으로 약 6조원을 벌어들인 셈이다.

같은 기간 삼성전자 비메모리 사업(시스템LSI+파운드리) 전체 매출규모인 4조3000억원을 훌쩍 뛰어넘는 기록이다.

선단 공정 수요처가 대부분 하이엔드 스마트폰용 AP 물량인데, AP는 다른 반도체들보다 빨리 시장에 출시하는 게 중요한 제품이다. 이 때문에 한두달이라도 양산이 빠른 파운드리 업체가 물량을 독식할 수 밖에 없는 구조다.

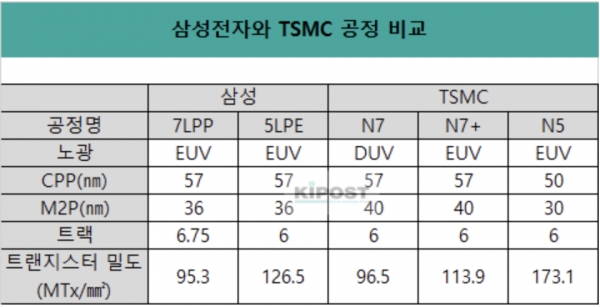

특히 양산 시점이 늦은데 트랜지스터 밀도 등 성능에 중요한 팩터들까지 삼성전자가 TSMC에 뒤쳐졌다. 시장조사업체 아이씨널리지(IC Knowledge)에 따르면 TSMC 5nm 공정(N5)의 트랜지스터 밀도는 173.1MTx/㎟다. 이에 비해 삼성전자 5nm 제품(5LPE)은 126.5MTx/㎟에 그친다. 7nm 제품 역시 TSMC 제품이 약 1.2배 밀도가 높았는데 5nm에서 그 차이가 더 벌어진 것이다. “삼성전자 5nm 공정을 쓰느니 TSMC N7+를 쓰는 게 더 낫다”는 고객사가 나오는 이유다.

한 파운드리 협력사 대표는 “현재로서는 삼성전자 파운드리의 선단 공정이 속도⋅밀도⋅수율 등 어느 하나라도 TSMC에 앞서는 게 없다”고 말했다.

삼성전자 첫 GAA 공정, TSMC는 3nm도 핀펫

이 때문에 3nm 공정은 삼성전자가 적어도 성능에서만큼은 TSMC에 대적해 볼 수 있을 계기를 마련해 줄지 귀추가 주목된다. 내년에 양산할 4nm 제품이 사실상 TSMC의 5nm에 대응하기 위한 제품이어서 진짜 승부는 3nm에서 갈리게 된다.

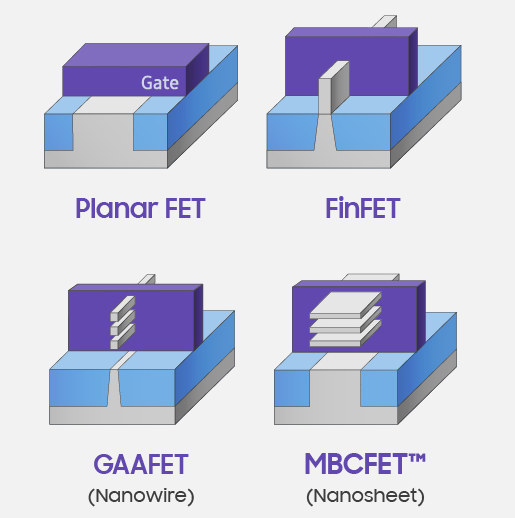

삼성전자는 3nm 공정부터 게이트가 채널을 4면으로 감싸는 ‘케이트올어라운드(GAA)' 기술을 도입한다. 이에 비해 TSMC는 3nm 역시 현재의 핀펫 기술을 적용하기로 했다. GAA와 핀펫의 가장 큰 차이는 게이트와 채널의 접촉면이 4면(GAA)이나 3면(핀펫)이냐다.

게이트⋅채널 간 접촉면이 많을수록 전류의 흐름을 효과적으로 제어할 수 있다. 전류 제어력이 좋아지면 트랜지스터를 동작하기 위해 필요한 게이트 전압 값도 줄어든다. 이는 GAA가 전력소모량을 절감할 수 있는 비결이다.

삼성전자 공식 발표에 따르면 GAA 기술을 적용할 경우, 7나노 핀펫 대비 칩 면적을 45% 줄일 수 있다. 또 소비전력은 50% 절감하면서 칩 성능은 35% 향상될 것으로 기대된다.

삼성전자가 GAA 기반 3nm 공정을 성공적으로 개발하고, 양산을 TSMC와 비슷하게 출발한다면 충분히 승산이 있다고 보는 이유다. 한 반도체 소재 업체 대표는 “삼성전자도 4nm까지는 TSMC에 대적하기 어렵다는 것을 통감하고 있다”며 “3nm 공정에서 진짜 승부를 벌여 보겠다는 심산”이라고 설명했다.