트랜지스터 밀도 '2.5억/mm'

TSMC가 최근 3nm 공정의 세부 사항을 공개했다. 21일 중국 콰이커지는 위키칩퓨즈를 인용해 TSMC는 트랜지스터 밀도를 2억5000만 개/mm로 목표하고 있다고 보도했다.

TSMC의 7nm EUV 공정으로 만든 화웨이의 '기린990 5G' 프로세서는 113.31mm 였으며 트랜지스터 밀도가 103억 개 였다. 평균 0.9억(9000만 개)/mm 수준이다.

이와 대조했을 때 3nm 공정 트랜지스터 밀도는 7nm 공정 대비 3.6배가 높다고 중국 언론은 분석했다. 이 밀도를 형상화하면 펜티엄4 프로세서를 바늘 크기로 축소시키는 것이라고 비유했다.

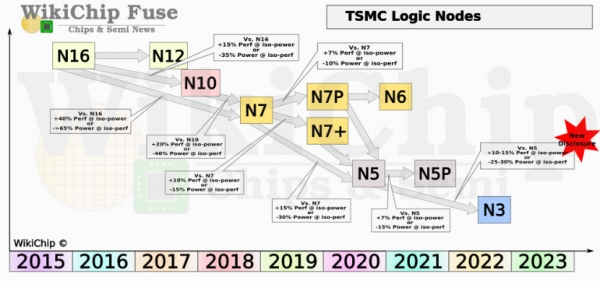

성능 관점에서 TSMC의 5nm는 7nm 성능 대비 15% 높아지고 전력 효율은 30% 개선했다. 하지만 3nm는 5nm 대비 성능이 7% 높아지며 전력 효율은 15% 높아진다.

이외 TSMC는 3nm 공정 연구개발이 예측에 부합하고 있다고도 전했다. 코로나19 영향도 없으며 2021년 위험생산 단계를 지난 2022년 하반기 양산 가능하다는 입장이다.

공정상 TSMC는 여러 옵션을 테스트한 결과 현재의 핀펫(FinFET) 공정이 원가와 효율상 우세하다고 판단, 3nm 첫 제품 역시 핀펫 트랜지스터 기술을 사용할 것이라고 전했다.

하지만 TSMC의 경쟁사인 삼성전자는 3nm 노드 발전 속도가 빨라 핀펫을 뛰어넘어 GAA로 직행할 수 있다고 언급했다.

TSMC의 5nm 공정 수율은 비교적 긍정적인 상황인 것으로 전해졌다. TSMC는 5nm 양산 이후 연구개발의 중점을 3nm에 두고 있다.

TSMC는 지난 16일 열린 1분기 실적보고회 컨퍼런스콜에서 3nm가 5nm 이후 칩 공정에 있어 완전한 진화가 이뤄질 것이며 1세대 5nm와 비교했을 때 1세대 3nm 공정의 트랜지스터 밀도가 70% 높아지고 속도가 10~15% 빨라지는 한편, 칩 성능이 25~30% 강화할 것이라고 밝혔다.