FPGA, ASIC, SoC 기반 비전 시스템 설계 및 구현 위한 픽셀 스트리밍 알고리즘 제공

매스웍스는 매트랩(MATLAB)과 시뮬링크(Simulink)의 릴리스 2019b(이하 R2019b)에 포함된 '비전 HDL 툴박스(Vision HDL Toolbox)'에서 프로그래머블반도체(FPGA) 상에서의 HFR(High Frame Rate) 및 고해상도 영상 처리를 위한 네이티브 다중 픽셀 스트리밍을 지원한다고 27일 밝혔다.

'비전 HDL 툴박스'는 영상·이미지를 처리하는 엔지니어나 FPGA 설계 엔지니어가 4K·8K 영상, 초당 240프레임(fps) 이상의 고해상도 영상 데이터를 처리할 때 시스템 동작 및 구현 간의 트레이드 오프(Trade-off)를 탐색 및 시뮬레이션하는 작업을 가속화하도록 돕는다.

FPGA 설계 엔지니어는 산업용 검사, 의료 영상, 정보, 감시 및 정찰(ISR) 등의 시스템에서 고해상도 및 HFR 영상을 실시간 처리하기 위해 처리량, 리소스 사용량 및 전력 소비량 목표를 충족시켜야 한다.

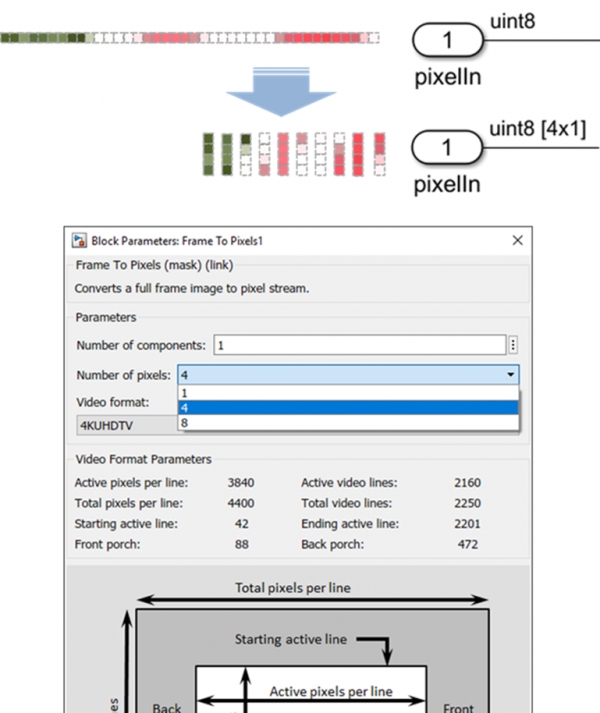

비전 HDL 툴박스는 FPGA, 전용반도체(ASIC) 및 시스템온칩(SoC) 장치에서의 비전 시스템 설계 및 구현을 위한 픽셀 스트리밍 알고리즘을 제공한다. 4 또는 8픽셀을 병렬 방식으로 처리하는 블록을 제공, 지정된 병렬 처리로 시뮬레이션·코드 생성을 수행하도록 하드웨어 구현을 자동적으로 업데이트한다. 이같은 기능은 하드웨어 엔지니어가 이미지·영상 처리 엔지니어와 협업을 통해 높은 추상화 수준에서 비전 처리 하드웨어 동작을 탐색 및 시뮬레이션할 수 있게 한다.

또 설계 과정에 다양한 유형의 인터페이스, 프레임 사이즈 및 프레임 레이트(frame rates) 세트를 활용할 수 있다. 툴박스에 탑재된 영상 및 이미지 처리 알고리즘은 지연 시간, 제어 신호 및 라인 버퍼를 비롯한 하드웨어 구현을 모델링할 수 있다. 이 때 HDL 코더를 추가, 검증된 상위레벨 모델로부터 직접 결합 가능하며 타깃 독립적이고 최적화된 VHDL 또는 베릴로그(Verilog) 코드를 생성할 수 있다. 생성된 HDL 코드는 FPGA 상에서 최대 8k 해상도의 프레임 및 HFR 영상을 처리할 수 있도록 검증됐다.

매스웍스의 수석 제품 마케팅 매니저 잭 에릭슨(Jack Erickson)은 “FPGA, ASIC 및 SoC 디바이스에서 비전 처리 알고리즘을 구현하는 데 있어 처리량과 리소스 사용량 사이의 현명한 절충은 필수적이지만 4K·8K 및 HFR 영상은 이러한 최적화를 더욱 어렵게 만든다”며 “비전 HDL 툴박스는 높은 추상화 수준에서 솔루션 공간을 탐색하고 시뮬레이션을 수행하는 기능을 통해, 엔지니어들이 RTL(Register-Transfer Level) 검증 및 확정 이전 아키텍처 상에서 보다 민첩하게 협업할 수 있도록 지원한다"고 말했다.