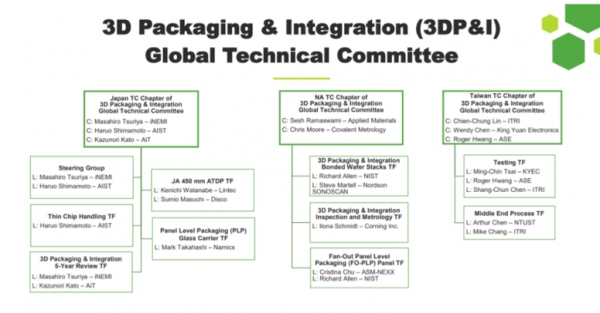

SEMI PLP 패널 TF, 패널 사이즈 2개로 압축… FOUP 및 캐리어 표준화도 시작

생산성은 높지만 수요와 성능은 아직… 이기종 패키징 및 적층 기술 확보 필요

반도체 패널레벨패키지(PLP) 시장 확대의 발목을 잡아온 생태계 문제가 해결될 조짐을 보인다. 세계반도체장비재료협회(SEMI) PLP 패널 태스크포스(TF)가 최근 패널 사이즈를 2개로 압축하면서다.

물론 이를 계기로 PLP 시장이 성장할 것이라고 예단하기는 어렵다. 가장 큰 장벽은 수요가 마땅치 않다는 것이다. 어느곳도 선뜻 대규모 투자를 하지 않는 건 이 때문이다.

SEMI, PLP 표준 사이즈 두 개로 압축

최근 SEMI PLP 패널 TF는 표준안에 넣을 PLP 패널 사이즈를 510㎜×515㎜ 및 600㎜×600㎜로 특정하고 참여 업체를 대상으로 투표를 진행 중이다.

당초 올해 상반기 표준안을 내놓기로 했지만 510㎜×515㎜ 사이즈를 밀고 있는 인텔과 600㎜×600㎜ 크기를 이미 채택한 외주 반도체 후공정(OSAT) 업체들이 팽팽히 맞서면서 결정이 늦어졌다. TF는 SEMI 내 PLP 관련 표준화 그룹들이 본격적으로 활동할 수 있도록 연말까지 표준안을 확정, 보급할 예정이다.

PLP는 실리콘 웨이퍼에 만들어진 반도체들을 인쇄회로기판(PCB)처럼 큰 패널에 올려두고 한 번에 패키징하는 기술이다. 개별 포장이 아닌 합포장으로 패키지 단가를 크게 낮춰줄 수 있는 기술로 주목받았다.

하지만 각 업체마다 활용하는 패널 크기가 달라 패널 공급사는 물론 장비 업체들도 6~7개의 패널 사이즈에 맞춰 제품을 개발해야했다. PLP 생태계가 좀처럼 커지지 못했던 건 이 때문이다.

패널 사이즈가 특정되면 패널을 놓을 캐리어와 이동식 저장장치(FOUP)부터 장비까지 관련 부품·장비 개발 및 생산을 한층 더 수월하게 할 수 있다. 나아가 가격도 저렴해진다.

SEMI PLP 패널 저장장치(FOUP) TF 산하 글로벌 물리 인터페이스 및 캐리어 기술위원회는 패널 TF의 표준안으로 FOUP 및 로드포트(LP) 인터페이스 등을 포함한 표준안을 개발할 계획이다.

일본 SEMI 산하에 조성된 PLP 글라스 캐리어(Glass Carrier) TF도 본격 활동을 준비하고 있다. 지난 6월 구성된 이 TF는 나믹스(Namics Corporation), 코닝, 아사히글라스(AGC) 등이 이끌고 있다. 이 TF에서는 내년 2월까지 캐리어 크기와 두께 등을 담은 표준 제안서를 낼 예정이다.

수요도, 성능도 발목

그렇다고 PLP 시장이 급격히 커질 수 있는 건 아니다. 어중간한 성능과 가격으로 좀처럼 수요가 없다. PLP 업체들은 물론 어플라이드머티어리얼즈(AMAT) 같은 글로벌 장비 업체들도 이 시장을 관망하고 있는 이유다.

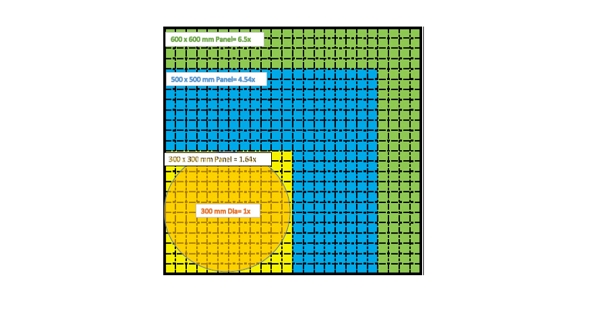

PLP 기술의 가장 큰 장점은 생산성이다. 스태츠칩팩(STATS ChipPAC)과 루돌프테크놀로지의 논문에 따르면 가로·세로 각 600㎜ 패널에서 패키지를 하면 300㎜ 웨이퍼에서 했을 때보다 6.5배 많은 다이(die)를 처리할 수 있다.

문제는 이정도 생산성을 요구할 정도로 생산량이 많은 단일 품목의 반도체가 드물다는 점이다.

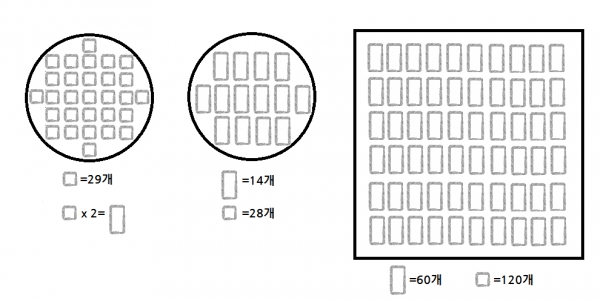

모바일 애플리케이션프로세서(AP)만 해도 그렇다. 1년에 출하되는 스마트폰을 15억대로 가정하고 그 속에 들어가는 AP가 모두 같다고 가정해보자.

AP 크기를 가로·세로 10㎜로 치면 300㎜ 웨이퍼로는 단순 계산으로 총 214만2900여번의 패키징 공정을 수행해야한다. 가로·세로 600㎜ 패널로는 42만번만 하면 된다. 월 처리량이 똑같이 40만장이라면 PLP 생산 라인은 한달 남짓에 일을 끝내는 반면, 웨이퍼 기반 후공정 라인에선 5개월하고도 보름이 더 걸린다.

실제 1년에 서로 크기와 사양이 다른 AP가 십수개 출시된다는 점을 감안하면 PLP에 쓰기엔 수량이 턱없이 부족한 셈이다.

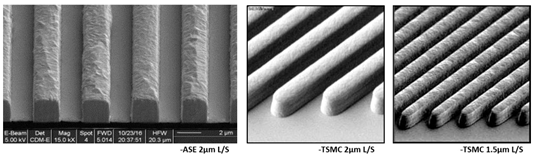

여기에 기존 패키지 기술보다 성능도 나오지 않는다. 모바일 AP처럼 고사양 반도체를 패키지하려면 적어도 밀도 성능을 뜻하는 L/S(Line and space)가 2/2㎛는 나와야한다. 내년에는 1/1㎛까지 요구 사양이 높아진다는 얘기도 나온다.

하지만 PLP는 기술력이 가장 뛰어난 삼성전자조차 L/S를 최대 7~8㎛ 정도까지밖에 구현하지 못한다. 연구개발(R&D) 단계에서는 2㎛ 구현에 성공했으나 수율 확보에는 수년이 걸릴 것으로 보인다.

특히 개별 다이를 패널 위에 옮기는 픽앤플레이스(Pick-and-Place) 공정이 어렵다. 처리량을 높이면서 정밀도를 확보하기가 쉽지 않기 때문이다.

몰딩 재료(Molding Compound)로 인한 패널 휨(Warpage) 현상과 봉지(encapsulation) 공정에서 다이가 원래 위치에서 벗어나는 다이 시프트(die shift) 현상도 아직 완전히 해결하지 못했다.

단위 생산량이 많으니 문제는 더 커진다. 웨이퍼로는 장당 수 개에 불과했던 불량품이 패널에서는 수십개가 나온다. 어떤 불량이느냐에 따라 패널에 있는 반도체 전체를 버려야할 수도 있다.

업계 관계자는 “PLP 자체가 PCB와 패키지 사이에 있는 기술이라 장비 성능 또한 반도체 패키지 장비보다 떨어지고 PCB 장비보단 높은 수준”이라며 “좋은 장비는 거의 개발부터 PLP 제조사가 함께 해야하고 가격도 ‘부르는게 값’”이라고 말했다.

이기종·적층… PLP가 가야할 길

단일 품목의 반도체만 PLP로 하면 승산이 없다. 단일 품목을 하려면 비싸고 처리량도 많지 않은 고밀도 패키지나 값싸고 이미 충분한 생산 용량(Capacity)을 가진 저밀도 패키지와 경쟁해야하는데 성능도, 가격경쟁력도 아직이다.

일단 PLP는 생산라인 구축에만 적어도 1000억원 가량이 들어가고 수율도 높지 않다. 생산량이 많다지만 저가형 PLP를 기준으로도 공정 단가가 플립칩(FC)과 비슷한 수준이다.

업계 관계자는 “볼그리드어레이(BGA) 등 구 패키지 기술은 수율이 100%나 다름없다”며 “굳이 안정화된 값싼 기술을 놔두고 PLP를 할 이유가 없다”고 설명했다.

남은 건 서로 다른 공정에서 생산된 다양한 반도체를 하나의 패널 위에 놓고 패키징하는 이기종(Heterogeneous Integration) 기술을 적용하는 것이다.

PLP에 이기종 기술을 적용했을 때의 이점은 명확하다. 2.5D 반도체처럼 이기종 반도체들을 양 옆으로 붙이는 경우 패키지가 직사각형 모양이 되는데, 웨이퍼는 원형이기 때문에 따로 생산했을 때보다 단위당 생산량이 적을 수밖에 없다. 반면 패널은 기본적으로 사각형이라 생산량 저하의 문제가 없다.

프라운호퍼 연구소에 따르면 패키지 사이즈가 클 경우 웨이퍼의 최대 면적 활용률(팬아웃)은 45%까지 떨어진다. 반면 패널은 패키지 크기와 상관 없이 최대 95%의 면적을 활용한다.

기판 위에 바로 여러 반도체를 패키징하기 때문에 인터포저(Interposer) 같은 값비싼 중간 기판도 필요 없고, 패키지 두께도 줄일 수 있다.

PLP에서 이기종 통합을 구현하는 방법은 여러 가지다. 패널 영역을 쪼개 영역별로 서로 다른 반도체를 두고 순서대로 패키징하는 비교적 단순한 방법부터 서로 다른 반도체들을 교차 배열해 아예 이기종 통합 패키지를 만드는 고차원적인 방법도 있다.

PTI·네패스 등 저밀도 반도체를 겨냥한 OSAT 업체들은 주로 전자를 개발 중이다. ASE는 데카(Deca)의 특허를 기반으로 600㎜×600㎜ 크기 패널을 가로·세로 300㎜씩 쪼개 서로 다른 반도체를 패키지하는 기술을 개발 완료했다.

삼성전자처럼 고밀도 반도체를 겨냥한 업체들은 후자를 연구개발(R&D)하고 있다.

최근 개최된 국제웨이퍼레벨패키지컨퍼런스(IWLPC)에서 삼성전자는 차세대 PLP 제품이 웨어러블용이며 이전 갤럭시워치에 들어간 제품보다 더 많은 기능을 포함하고 있을 것이라고 시사했다. 삼성이 작년 생산했던 PLP 제품은 AP와 전력관리반도체(PMIC)를 결합한 것이었다.

ASE도 데카 기술이 아닌 자체 기술로 개발한 FoCoS(Fan-Out Chip on Substrate)를 PLP 라인에서 양산할 준비를 하고 있다. FoCoS는 HBM, 프로세서처럼 고밀도 반도체를 기판 위에 직접 패키징하는 기술이다. 이를 통해 인공지능(AI), 5세대(5G) 이동통신 네트워크 시장을 공략하겠다는 것이다.

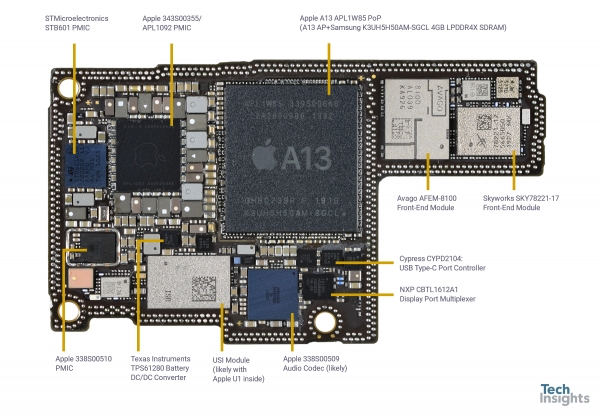

패키지 위에 패키지를 쌓는 패키지온패키지(PoP), 칩을 쌓는 3D 적층 기술 또한 개발돼야한다. 이렇게 되면 스마트폰 등 전자기기에 들어가는 메인 보드 자체를 PLP 공정에서 만들 수 있게 된다.

김성동 서울과학기술대학교 기계시스템디자인공학과 교수는 “PLP는 “아직 수율이 낮아 웨이퍼레벨패키지(WLP)가 단연 압도적”이라며 “PLP는 3D 패키지나 PoP를 해야 가격 경쟁력이 있다”고 말했다.