TSV는 연결 밀도 늘리기 어렵고 공정 비용도 비싸… HBM 개당 최소 50달러

M3D는 CMOS 공정 전공정(FEOL)에서 진행… 레이저 어닐링·본딩 기술 핵심

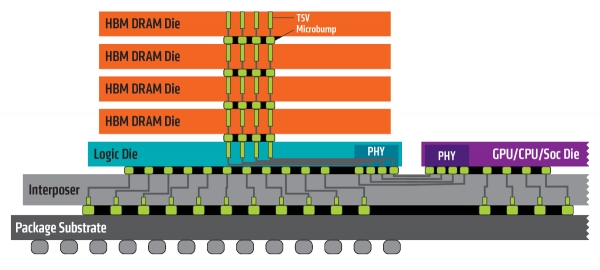

그동안 한정된 공간에 반도체를 수직으로 쌓아 올리는 데 필요한 대표 기술은 실리콘관통전극(TSV)이었다. D램 다이(die)를 층층이 쌓아 메모리 대역폭과 용량을 늘린 고대역폭메모리(HBM)에도 TSV가 쓰였다.

하지만 TSV 기반 3D 적층 기술로 성능을 높이는 데도 한계가 있다. 이에 모놀리식 3D 등 차세대 적층 기술 연구개발(R&D)이 본격화되고 있다.

현 3D 적층 기술의 한계

가장 최근 상용화된 3D 적층 기술은 TSV다. HBM과 3D 상보성금속산화물반도체(CMOS) 이미지센서(CIS)가 이 TSV 기술을 활용해 만들어진다.

TSV는 전공정을 끝낸 반도체 다이(die)를 적층한 후 구멍(via)을 뚫고 구리를 채워 레이어와 레이어, 반도체와 반도체를 전기적으로 연결하는 통로를 만드는 기술이다. 이 통로가 넓고 많을수록 전체 성능이 올라가는데, 현재 TSV는 구멍의 두께가 최소 수 마이크로(㎛) 수준으로 두꺼워 구멍을 많이 뚫기 어렵다.

TSV를 활용하면 패키지 크기는 줄일 수 있지만, 실리콘 다이 자체의 크기가 커지는 것도 같은 이유다. 패키지 크기가 줄어드는 건 2D로 반도체들을 배치했을 때 지연시간을 줄이기 위해 반도체 사이에 삽입하는 리피터(Repeater)가 없기 때문이다.

공정 비용도 만만치 않다. HBM과 그래픽처리장치(GPU)를 2.5D 패키지로 묶은 제품의 원가 구조를 살펴보면 D램의 TSV 적층에만 개당 16~20달러가 들어간다. 다이와 다이를 정확한 위치에 놓기도, 두꺼운 구멍을 위에 있는 다이의 상단부터 아래 있는 다이의 하단까지 균일하게 뚫기도 쉽지 않아서다.

TSV에 필요한 재료인 실리콘 인터포저는 이보다 1.5배 더 비싸다.

TSV를 잇는 차세대 3D 적층 기술, M3D

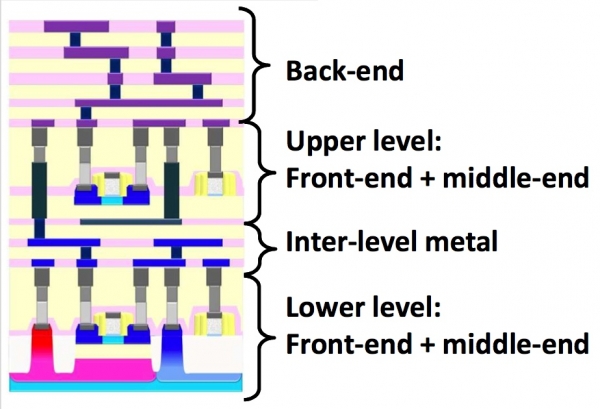

M3D는 서로 다른 공정에서 생산된 여러 반도체를 마치 3D 낸드의 셀을 쌓듯 적층하는 기술이다.

후공정에서 진행돼 구멍이 큰 TSV와 달리 M3D는 전공정(FEOL)에서 진행돼 트랜지스터나 게이트 수준에서 3D를 구현한다.

기존 CMOS 공정을 활용하기 때문에 설비투자 비용이 적게 들고 TSV보다 수십분의 1 수준으로 작은 구멍(Inter-layer via)을 촘촘히 만들 수 있다. 즉 TSV 대비 구멍을 수백배 많이 형성할 수 있고, 이를 통해 전력소모량은 줄이고 대역폭은 늘릴 수 있다.

조지아공대 임성규 교수의 연구결과에 따르면 14나노 핀펫(FinFET) 공정으로 생산된 반도체를 기준으로 M3D(0.1㎛)는 2D 평면 배치 대비 면적(Footprint)은 절반, 배선으로 인한 전력 소모량은 20%(전체 전력 소모량은 9% 감소) 줄일 수 있었다.

TSV(5㎛)로 적층하면 면적은 2D보다 12% 줄어들었고, 오히려 실리콘 다이 면적은 76% 증가했다. 배선 전력 소모량은 15%, 전체 전력소모량은 4% 각각 커졌다. TSV에서 996개였던 비아의 개수는 M3D에서 4만9000여개로 늘었다.

M3D 구현의 발목을 잡던 공정 기술

지난 2012년 조지아공대에서 처음 제안한 후 퀄컴·삼성·Arm·레티(CEA-Leti)·인텔 등이 본격적으로 연구개발을 시작했다. 하지만 연구소를 제외한 각 업체들은 공정 기술이 발전되지 않았다는 이유로 곧 연구개발(R&D)을 중단했다.

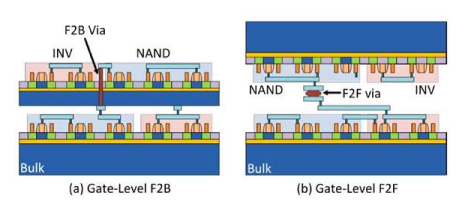

M3D는 각각 트랜지스터 형성을 마친 두 웨이퍼, 혹은 웨이퍼와 다이를 본딩(Bonding) 기술로 붙이거나(F2F) 하나의 웨이퍼에 트랜지스터를 만든 다음 그 상태 그대로 위에 다른 반도체 제조 공정을 순차적으로 진행하는(F2B) 두 가지 방식으로 나뉜다.

F2F 방식에서는 본딩 공정에서 웨이퍼를 얼마나 정확히 원하는 위치에 놓고 붙일 수 있는지에 따라 활성층 구멍의 크기를 조절해야했다. 정확도가 떨어지면 구멍을 크게 만들어야해 기존 TSV·범프 기술과 큰 차이가 없었다는 얘기다.

F2B 방식은 트랜지스터 위에 트랜지스터를 만들기 때문에 아래 위치한 트랜지스터 위에 단결정 실리콘으로 구성된 활성층(Active layer)을 만들어야 했는데, 반도체 제조 공정에서 널리 쓰이는 화학기상증착(CVD) 공정으로는 형성이 불가능했다.

또 상부 트랜지스터를 만들 때 1000℃ 이상의 고온 공정을 진행하면 하부 트랜지스터의 배선 금속이 녹아버리는 문제도 있었다.

해결책의 실마리가 잡혔다… 핵심은 레이저 어닐링과 본딩

현재는 F2B 방식의 M3D를 중심으로 해결책의 실마리가 잡혔다.

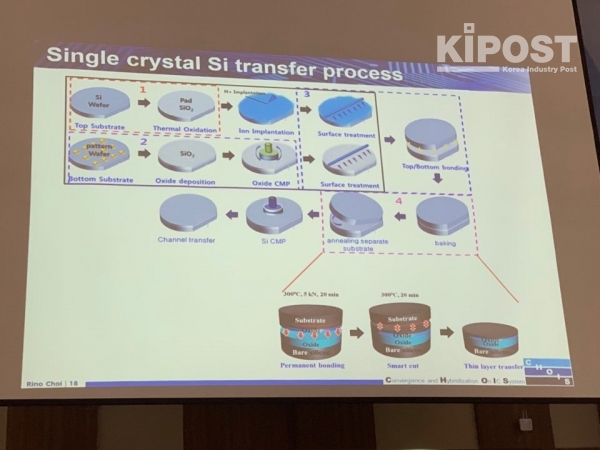

먼저 단결정 실리콘 활성층은 두 가지 해결책이 나왔다. 트랜지스터 위에 다결정 실리콘 박막을 플라즈마 CVD(PECVD)로 증착하고 이를 결정화하거나 별도로 만든 단결정 기판을 기존 웨이퍼 위에 전사(Transfer)하는 방법이다.

다결정 실리콘 층을 단결정 실리콘 층으로 바꿀 때는 레이저 어닐링(Laser annealing) 기술이 쓰인다. 기존 단결정 실리콘 형성 방법과 달리 순식간에 표면을 1000℃ 이상으로 올릴 수 있어 아래 트랜지스터 층이 받는 스트레스를 줄일 수 있다. 해당 층에서 소스와 드레인의 불순물을 활성화하는 것도 레이저 어닐링 기술이다.

기판 전사 방법에서는 실리콘온인슐레이터(SOI) 기판이나 특정 이온을 주입해놓은 기판을 활용한다.

SOI 기판은 아래 기판(Substrate)과 위 실리콘(Si) 층 사이 절연층이 있는데, 트랜지스터가 형성된 웨이퍼에 SOI 기판을 거꾸로 엎어놓고 화학적 식각을 하면 기판만 떼어낼 수 있어 얇은 실리콘 층만 남길 수 있다.

이온 주입 방식은 스마트컷(Smart cut) 기술로도 불리는데, 벌크 웨이퍼에 수소 등의 이온을 주입하면 실리콘 내부로 들어가 특정 깊이에 있는 격자를 파괴해 얇은 실리콘 막을 박리하는 데 활용되던 기술이다. 격자구조와 표면이 울퉁불퉁하다는 게 단점이었지만, SOI 기판 업체 소이텍이 화학기계연마(CMP)로 표면을 다듬고, 레이저 어닐링으로 결정구조를 복구하는 특허를 출원하면서 가닥이 잡혔다.

두 기판을 서로 붙이는 본딩 기술도 해결 방안이 나왔다. 기존 웨이퍼-웨이퍼 본딩 기술은 열압착본딩(TCB)을 활용했는데, TCB는 처리량(throughput)이 적은데다 고온에서 압력을 가해 트랜지스터와 실리콘 층에 스트레스를 줬다.

업계에서는 TCB 대신 유전체와 유전체, 금속과 금속이 상온에서 화학적으로 결합하는 하이브리드 본딩(Hybrid bonding) 기술이 유용하게 쓰일 것으로 보고 있다. 표면 관리가 까다롭지만 이미 3D CIS 제조에서 활용되고 있는 기술이라 상용화가 어렵진 않다.

최리노 인하대 교수는 “M3D는 기반 기술이 어느 정도 확보된 상황으로, 응용처를 찾는 게 과제”라며 “3D CIS처럼 3D 적층의 이점이 분명한 응용처에 선적용될 것”이라고 말했다.