In addition to the new support of its RTG4™ high-speed signal processing radiation-tolerant FPGA family for aerospace markets, Libero SoC v 11.6 also offers enhanced features for Microsemi's award-winning SmartFusion™2 SoC FPGAs andIGLOO™2 FPGAs.

"The release of Libero SoC v 11.6 enhances ease of use for double data rate (DDR) and high-speed serial designs, with improved configurators and design efficiency improvements in global assignments and register retiming—resulting in faster time-to-market for designers of FPGA-based solutions," said Shakeel Peera, senior director of FPGA/SoC marketing for Microsemi.

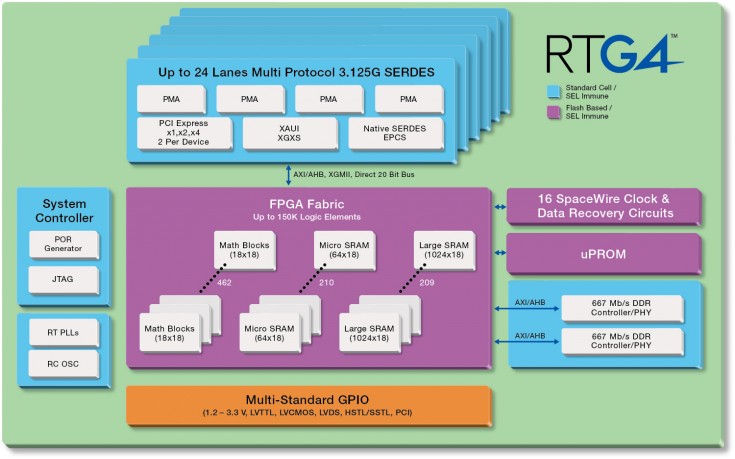

"RTG4 support now includes IO Advisor, SmartPower and uProm support, and takes advantage of other design optimization improvements in this release, demonstrating Microsemi's commitment to the space industry as the leading provider of FPGAs for the space market."

Microsemi's new Libero SoC v11.6 release automatically optimizes hold violations using minimum delay repair and provides advanced multi-pass options in layout for large designs. It optimizes power consumption with a new IO Advisor that reduces input and bi-directional I/O power.

The new release also offers greater design efficiency with an improved design hierarchy browser and text editor features. In addition, it extends customer access to the advanced features of Microsemi's security devices by including them in the freeLibero Gold license.

Other features include:

- SmartPower interface support for RTG4 design-specific power analysis

- SmartDebug interface support for Serializer/Deserializer (SerDes) and DDR blocks in SmartFusion2, IGLOO2 and RTG4

- Place and route improvements in carry chain clustering and logic packing, resulting in a higher quality of results (QoR) with increased routability for larger designs

- New multi-pass place and route options, which provide advanced control for difficult timing closure designs

"The SmartFusion2 and IGLOO2 families provide powerful differentiated silicon platforms," said Stefan Schutz, CEO and General Manager of Solectrix GmbH. "When combined with the productivity and ease of use gains that Libero SoC 11.6 release provides, it completes an excellent ecosystem for our developers to get to market quickly with mainstream industrial networking and imaging applications like the SXoM-SF2 solution from Solectrix GmbH."

Additionally, Avnet, Inc., a leading global technology distributor, recently introduced a new SmartFusion2 KickStart Kit with Microsemi which utilizes the new Libero v 11.6 software.

"For Avnet's SmartFusion2 KickStart board, which features a secure M2S010S SoC, Libero 11.6 now allows use of the secure features with the free Gold licenses from Microsemi," said Tom Curran, technical marketing engineer, Avnet Electronics Marketing. "The tool flow is smooth, compilation times are down and productivity is up."

According to the Aberdeen group, by the year 2020 approximately 50 billion machines will be connected. Not only do these machines need to be secure, they need to be secured at the device, design and system levels. To enhance access for FPGA designers worried about secure FPGA designs, Libero v 11.6 introduces licensing changes to extend access for all users to popular security devices (005S and 010S) using the free Libero Gold license.