(Credit: Applied Materials) - In the latest edition of Chip Scale Review Applied Materials’ David J. Erickson, Global Product manager; Isaac Ow, Global Product manager; and Sesh Ramaswami, managing director, discuss optimizing TSV processes and integration for volume manufacturing in a technical feature article. Below is the introduction to the article.

Through-silicon via (TSV) technology creates new opportunities for numerous high-performance and/or form factor conscious applications and is used for devices such as DRAM, logic, and sensors, as well as for advanced silicon interposer applications in GPU, wireline communications, and high-performance computing.

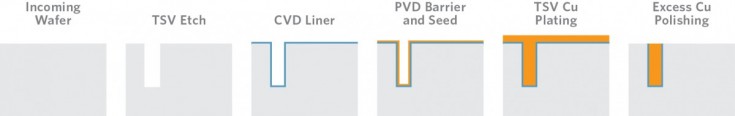

In both 3D and 2.5D architectures, the central element is the TSV itself, whose fabrication has been subject to many unit process and process-integration challenges that have now been largely resolved. The primary steps in forming the via are deep silicon via etch, chemical vapor deposition (CVD) of an insulating oxide liner, physical vapor deposition (PVD) of a metal barrier and seed layer, electrochemical deposition (ECD) of Cu, and chemical mechanical planarization (CMP) as shown in Figure 1. TSV aspect ratio (AR) typically ranges from 5:1 to 12:1.

In the via-middle flow, TSVs are created after transistor formation but before the formation of all or some of the back-end of-line (BEOL) damascene interconnect layers. Via-reveal is a companion process to via-middle and is done on the backside of wafers after thinning. In the via-last flow, TSVs are created from the backside of thinned wafers. Many applications integrating TSVs must also adopt new bumping approaches to meet the more challenging pitch and density requirements. TSV enabled die-to-die stacking of chips such as DRAM requires very high density bump arrays, presenting unique within-die co-planarity challenges.

The article goes on to review the requirements and new developments for each of the process steps in a typical integration flow.

Read the full article in Chip Scale Review for more details.

- Connie Duncan -