삼성·GF 내년 7나노 양산… 3나노부터는 구조 바뀐다

7나노 반도체 시대가 열렸다. 45나노가 최첨단 공정이던 게 2000년대 후반이었으니 10년만에 선폭이 6분의 1로 줄어든 셈이다.

앞으로 10년 후는 어떻게 될까.

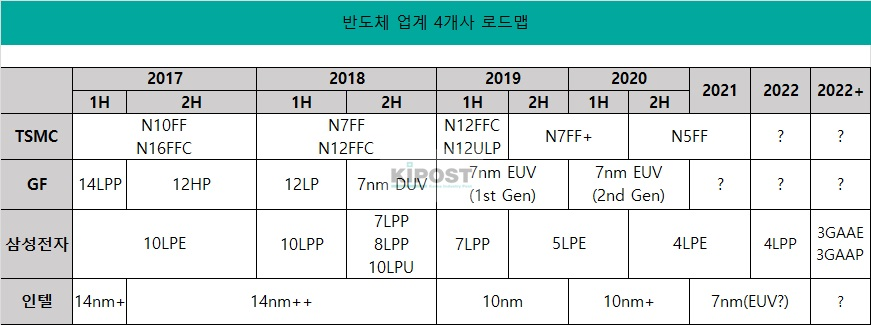

미세공정 경쟁을 벌이는 업체는 TSMC와 글로벌파운드리(GF), 삼성전자, 인텔 4개사다. 이들의 로드맵을 점검하고 향후 미세공정 추이를 가늠해본다.

7나노는 TSMC 먼저, 삼성·GF는 내년

현재 7나노 양산을 시작한 업체는 TSMC가 유일하다.

TSMC는 지난 4월 컨퍼런스콜에서 극자외선(EUV) 노광 없는 7나노 1세대 핀펫(FinFET) 공정 ‘N7FF’가 대량양산체제(HVM)에 돌입했다고 밝혔다.

이는 아직 EUV 관련 설계 및 공정자산(IP)이 충분히 갖춰지지 않았고, 기술의 안정성도 부족하기 때문인 것으로 분석된다. 순수 파운드리 업체 입장에서 양산성이 검증되지 않은 기술에 막대한 투자를 집행하기엔 부담이 크다.

TSMC는 내년 7나노 2세대 ‘N7FF+’ 공정에서부터 EUV를 도입할 계획이다. 이를 위해 최근 멘토그래픽스·케이던스 등 주요 반도체 설계자동화(EDA) 툴 업체들과 협력을 강화하고 있다.

내년에는 삼성전자와 글로벌파운드리가 7나노 양산에 돌입한다.

삼성전자는 EUV를 도입한 ‘7LLP(7㎚ Low Power Plus)’ 공정을 제공할 계획이다.

‘LLP’는 통상 삼성전자가 2세대 공정에 붙이는 이름이다. 1세대 명칭인 ‘LPE(Low Power Early)’가 붙지 않은 것은 EUV 공정을 차별화하기 위한 것으로 풀이된다.

1세대 5나노 핀펫 공정 ‘5LPE(5㎚ Low Power Early)’는 7나노 공정에 ‘스마트 스케일링(Smart Scaling)’ 기술을 적용한다. 작년까지 로드맵에 포함돼있었던 6나노 공정은 사라졌다.

1·2세대 4나노 핀펫 공정 ‘4LPE·LPP’는 5나노에서 ‘이지 마이그레이션(Easy migration)’ 작업을 거쳐 활용할 수 있게 할 예정이다. 7나노 기반으로 5나노, 4나노까지 가능하다는 얘기다.

글로벌파운드리는 당초 EUV를 활용해 7나노 반도체를 양산할 계획이었지만, 최대 고객사인 amd가 TSMC의 N7FF 공정을 활용하기로 하면서 1세대 공정에는 EUV를 도입하지 않기로 결정했다. (참고=>글로벌파운드리, EUV 도입 연기… TSMC에 맞추기로)

이 회사는 2020년 일부 층에 EUV를 적용한 7나노 2세대 및 3세대 공정을 선보일 계획이다.

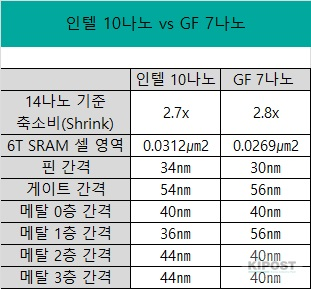

인텔은 내년 10나노 핀펫 공정을 양산한다. 인텔의 10나노 공정은 타사의 7나노 공정과 비슷한 성능을 낸다. 원래 올해 10나노 핀펫 공정을 양산할 예정이었지만, 수율을 끌어올리지 못해 계획이 미뤄졌다.

인텔은 10나노에 EUV 대신 로컬 인터커넥트 및 접점(Contact) 부분에 텅스텐(W) 대신 코발트를 활용하고, 확산막에 티타늄층을 추가한 3세대 핀펫 구조를 쓴다. 4번의 자동 정렬 패터닝(SAQP) 기술도 적용했다.

값비싼 EUV를 도입하는 대신 패터닝 기술을 정교화하고, 소재를 바꿔 기존 기술을 개선하는 데 주력하는 모습이다.

EUV는 연구개발(R&D) 차원에서 테스트 중이다. 10나노 및 7나노 마스크를 생산할 수 있는 파일럿 라인을 보유 중이지만, 아직 EUV를 언제 도입할지에 대해서는 밝히지 않았다.

업계 관계자는 “인텔이 내후년 2세대 10나노 공정에서는 EUV를 도입할 것”이라며 “타사가 7나노, 5나노 반도체를 양산하는데 인텔만 EUV 없이 10나노에 머무를 수는 없을 것”이라고 말했다.

로드맵 불확실… 양산 목표 밝힌 곳 삼성·TSMC 뿐

7나노 그 이후는 어떻게 될까. 4개사 중 5나노, 3나노에 대한 로드맵을 밝힌 곳은 삼성전자와 TSMC뿐이다.

삼성전자는 2020년까지 3나노 게이트올어라운드(GAA) 공정을 개발하겠다고 밝혔다.

TSMC는 올 초 대만 남부 사이언스파크(Southern Taiwan Science Park)에 5~3나노 반도체를 생산할 팹(Fab) 18을 착공했다.

팹 18에서는 내년 5나노 핀펫 ‘N5FF’ 공정의 시생산이 진행된다. 대량 양산 시점은 2020년 하반기다.

EUV를 처음 활용하는 ‘N7FF+’ 공정에서 마이그레이션(migration) 작업을 거쳐 5나노 공정을 활용할 수 있게 할 것으로 보인다. 1세대 ‘N7FF’ 공정 대비 성능 차이가 크지 않기 때문이다.

TSMC에 따르면 N7FF+ 공정은 N7FF 공정보다 게이트 밀도나 전력소모량은 개선할 수 있지만 속도는 빨라지지 않는다. 반면 5나노 공정은 전력 소모량이 N7FF 대비 65%에 불과하고 밀도는 3배나 높일 수 있다. 속도 또한 빠르다.

팹18 절반에는 3나노 생산 라인이 깔린다. 정확한 양산 시기는 밝히지 않았지만, 모리스 창 TSMC 최고경영자(CEO)는 팹18 기공식에서 3~4년 내 3나노 반도체를 양산할 것이라 밝혔다. 총 3단계(Phase 3) 투자까지 진행, 2023년 마무리된다.

글로벌파운드리는 이전 14나노에서 10나노를 건너뛰고 7나노를 양산하겠다고 했던 것처럼 7나노 이후 3나노로 직행하는 방안을 검토하고 있다. 5나노 공정보다는 3나노 공정의 투자 가치가 높다는 판단에서다.

톰 콜필드(Tom Caulfield) 글로벌파운드리 최고경영자(CEO)는 최근 한 언론사와의 인터뷰에서 “투자액을 감안하면 5나노 공정은 충분하지 않다”며 “완벽한 성능을 가지려면 3나노가 필요한데, 아직 둘 중 적합한 차세대 공정이 무엇이 될지는 결정하지 못했다”고 말했다.

5나노 이후 전략이 분명하지 않은 이유, 트랜지스터 구조가 바뀐다?

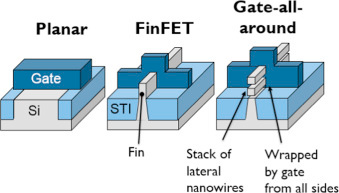

이처럼 업계가 5나노 이후의 로드맵을 좀처럼 확정짓지 못하고 있는 이유는 5나노 선폭까지 미세화됐을 때 기존 핀펫 구조로는 전류 누출을 막기 힘들기 때문이다.

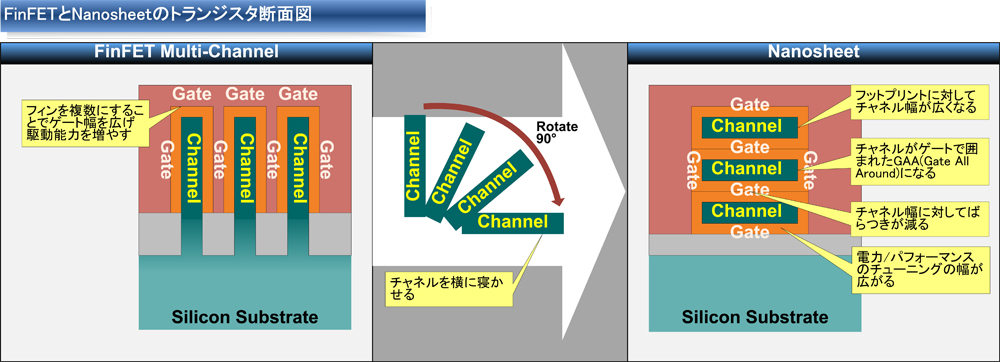

평평한(Planar) 2D 구조에서 핀펫(FinFET)으로 트랜지스터 구조가 바뀌었듯, 또다시 형태를 바꿔야한다는 얘기다. 삼성전자가 3나노부터 도입하는 ‘GAA’ 트랜지스터 구조가 대표적이다.

트랜지스터는 전자가 소스에서 드레인으로 이동하면서 움직인다. 전자가 이동하는 길을 채널이라고 한다. 채널에는 게이트라는 일종의 문이 있는데, 게이트와 채널이 만나는 면적이 넓을수록 전자의 흐름을 잘 제어할 수 있다.

핀펫 구조는 채널을 위로 튀어나오게 만들어(핀), 위와 양 측면에서 게이트와 만나게 했다. 인텔이 5나노 이후 차세대 기술로 트랜지스터 하나에 핀을 3개 형성하는 트라이게이트(Tri-gate) 핀펫을 연구개발 중이지만, 노광 공정이 복잡해진다는 한계가 있다.

반면 GAA 구조는 채널 가운데에 게이트에 통과시켜 게이트의 모든 면과 채널이 만나는 형태다. 얇은 튜브를 수직으로 세우는 나노와이어를 활용하거나 나노시트를 층층이 쌓아 구현한다.

삼성전자와 IBM, 글로벌파운드리(GF)는 지난해 나노시트를 활용한 GAA구조의 트랜지스터(FET)에 대한 연구결과를 발표했다. 핀펫이 채널 가운데를 튀어나오게 한 것이라면, 이들은 채널과 게이트 층을 눕혀 쌓아 GAA 구조를 만들었다.

업계에서는 삼성전자가 선제적으로 양산 계획을 밝힌만큼 나노 시트를 활용한 GAA가 차세대 트랜지스터 구조가 될 것이라 내다보고 있다. 노광 공정의 복잡성을 줄일 수 있고 핀펫보다 채널 폭을 넓혀 성능을 높일 수 있기 때문이다.

다만 아직 관련 설계 및 공정자산(IP)이 마련되지 않았고, 생산 설비도 개선이 필요한만큼 EUV를 도입한 7나노, 5나노 공정이 향후 3~4년간은 최첨단 기술로 자리잡을 것으로 전망된다.

업계 관계자는 “성능을 높이는 것도 중요하지만, 문제는 신기술 때문에 투자액이 급증한다는 점”이라며 “극자외선(EUV) 노광 기술도 해결되지 않은 부분이 많아 EUV 기술 도입 및 안정화를 위한 시간이 필요할 것”이라고 말했다.