7나노미터(nm) D램은 구현 가능할까. 소재나 공정을 바꾸지 않고도 10나노 이하 D램을 생산할 수 있는 후보 기술이 나왔다. 캐패시터(Capacitor)를 없애 공정 미세화를 앞당기고 제조 비용까지 45%까지 절감해주는 획기적인 방식으로, 상용화 될 경우 D램 시장 판도를 바꿀 것으로 예상된다.

킬로패스(대표 찰리 쳉)는 11일 서울 삼성동 그랜드인터컨티넨탈에서 기자간담회를 열고 '수직적층사이리스터(VLT, Vertical Layered Thyristor)' 기술을 발표했다.

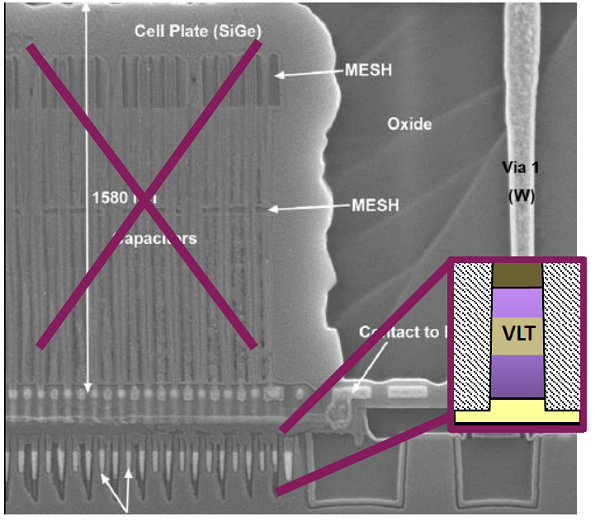

찰리 쳉 최고경영자(CEO)는 "D램 발전의 가장 큰 병목은 캐패시터"라며 "캐패시터는 부피가 큰데 반해 20nm 이하에서는 캐패시터 하나당 용량이 너무 작다"고 말했다. 20nm 공정의 트랜지스터 단면 면적은 30nmⅹ30nm인 반면 캐패시터는 55nmⅹ1000nm로 높아 물리적으로 무너지기 쉬운 구조다.

킬로패스가 착안한 아이디어는 캐패시터를 없애고, 트랜지스터 트렌치에 4층으로 이뤄진 소자구조를 적용하는 것이다.

VLT를 구현하기 위해서는 임플란트(박막 증착 기술 중 하나) 공정이 추가 된다. 식각(에칭)이 필요 없다는 것도 장점이다. 소자 구조만 바꿔주기 때문에 신소재나 장비가 필요 없다고 회사측은 설명했다.

|

| 찰리 챙 킬로패스 CEO. |

쳉 CEO는 "게이트 전류가 음극으로 흘러 도통(turn on)하는데 드는 시간은 10피코초(ps)로 빠르다"며 "0(전류 차단)과 1(전류 흐름) 사이 전압차가 1억배라, 다양한 환경에 맞는 회로 설계에도 적합하다"고 설명했다.

현재 D램 메모리는 상보성금속산화물반도체(CMOS) 공정을 사용하는 낸드플래시, 시스템반도체 공정보다 미세화 속도가 더디다. 현재 주력 생산 공정은 25nm고, 삼성전자가 내년 18nm D램을 양산하기 시작하면 처음으로 20nm 벽이 깨진다.

시스템반도체는 현재 14nm 생산이 이뤄지고 있고 올 연말부터 10나노미터(nm)를 양산할 계획이다. 낸드플래시는 3D화 되면서 미세화 이슈를 조금 빗겨가고 있지만 이미 지난해 15nm까지 선폭을 줄였다. D램이 이들보다 빠르게 미세화할 가능성이 열렸다.