[The Korea Industry Post(kipost.net)] 삼성전자는 지난 2013년 1세대 24단을 쌓은 3D낸드플래시를 출시한 이래 매년 단수를 높이면서 층고를 높여왔다. 올해는 64단 3D낸드플래시 양산을 시작했고, 올해 96단 개발을 완료하고 내년 생산에 돌입할 전망이다.

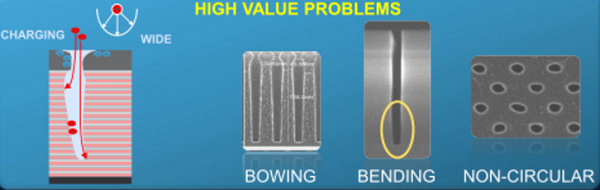

1~2년 후에 상용화할 100층 이상을 쌓은 제품도 개발 중인데, 실제 양산을 위해 극복해야 할 기술 과제가 여럿 있다. 각 층(레이어)이 현재 두께를 유지한다면 웨이퍼 한장 위에 쌓는 화학물질 층은 10마이크로미터(μm)까지 높아진다. 무게, 신호 전달 통로인 채널홀의 고종횡비(High Aspect Ratio) 등 수율을 떨어뜨리는 다양한 문제점이 발생할 수 있다. 다양한 물질을 증착해 박막을 형성하다보니 공정 시간(쓰루풋)이 너무 느리다는 단점도 있다.

램리서치가 다양한 난제를 풀 수 있는 해법을 몇 가지 내놨다.

웨이퍼 스트레스 컨트롤, 레이어 두께 계측 솔루션으로

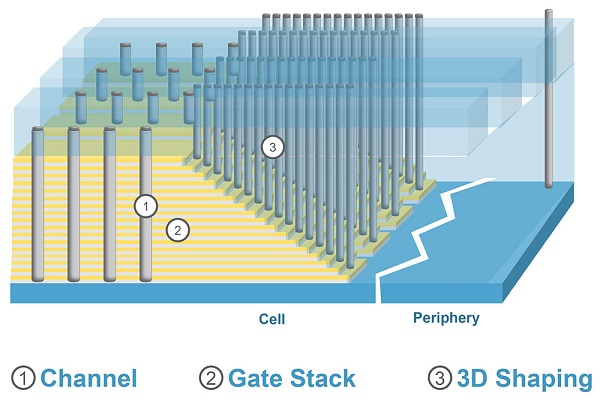

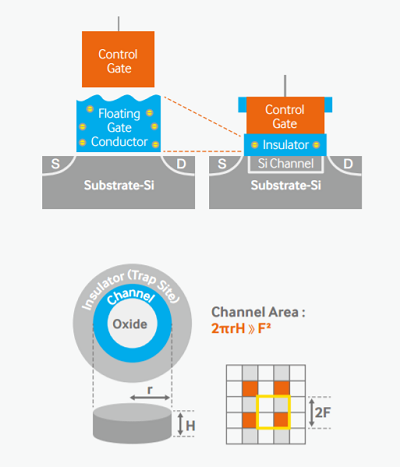

3D 낸드플래시는 웨이퍼 위에 수평방향으로 형성했던 비트라인(Bit line)과 수직방향으로 화학물을 쌓아 만들었던 워드라인(Word line)을 90도로 돌려 놓은 형태로, 워드라인 사이에 간섭을 막아주는 절연 물질을 채워야 한다. 단면을 보면 주로 금속 물질로 이뤄진 워드라인 층과 절연막 역할을 하는 산화막(옥사이드) 층이 번갈아 쌓여 있는 모습을 볼 수 있다.

이 때 한 층 한 층의 두께를 균일하게, 표면은 매끄럽게 쌓는 게 관건이다. 표면이 울퉁불퉁하면 다음 층을 쌓을 때 계속 영향을 주고, 두께가 다르면 각 셀(Cell)마다 전자 저장 공간이 차이가 난다. 그런데 다양한 물질을 한층 한층 쌓을 때마다 두께가 미세하게 변할 수 있다. 램리서치는 계측 솔루션을 개발해 자사 장비에 탑재했다. 레이어를 샇을 때마다 두께를 바로 측정해 오류를 수정할 수 있어 최종적으로 수율이 높아진다.

홍성현 램리서치 상무는 “스트레스 컨트롤 최적화가 중요하다”며 “장비, 공정, 소재 등을 모두 최적화 해야 하는데 그 방법 중 하나가 나이트라이드 필름을 이용한 계측 솔루션으로, 웨이퍼 무게가 미세하게 변하는 것을 측정해서 두께를 계측하는 것”이라고 설명했다.

고종횡비, 탄소(카본) 하드마스크로 해결

특히 층고가 쌓이면서 각 셀간 신호 이동 통로가 되는 채널 전극을 형성해야 하는데, 홀 직경은 늘지 않지만 길이가 늘어나기 때문에 고종횡비 문제가 생긴다. 업계는 100층 이상 3D 낸드플래시의 종횡비가 10대1까지 커질 것으로 예상한다.

이 수직 전극을 형성하려면 일단 식각(에칭)으로 매끈한 홀을 형성 시켜야 하는데, 중간에 빈공간(void)이 발생하거나 완벽하게 에칭이 되지 않는 경우가 생긴다.

이 문제는 에칭시 하드마스크를 개선하는 것으로 해결했다. 최근 하드마스크 두께는 1μm 정도인데 홀 깊이가 깊어질수록 하드마스크 두께도 두꺼워진다. 각 층의 화학물질에 두꺼운 하드마스크가 더 해지면 웨이퍼가 휠 가능성은 더 커진다. 하드마스크 두께를 줄일 수 있는 방법은 에칭 선택비를 높이는 것이다. 램리서치는 기존 비정질(아몰포스) 카본 하드마스크를 써 왔는데, 최근 카본 매트릭스에 금속(텅스텐)을 도핑한 카본 하드 마스크(MDLC)를 도입했다. 이 회사에 따르면 선택비가 기존 하드마스크 대비 3배 높아진다.

워드라인 증착 오류 줄이는 ALD 공정 도입

삼성전자는 워드라인(게이트)을 형성할 때 먼저 나이트라이드 막을 도포한 다음 이를 제거하고 화학적 기상증착(CVD)를 이용해 텅스텐을 주입하는 ‘Gate Last’ 방식을 쓴다. 이때 나이트라이드를 제거하기 위해 불산(플루오린)을 이용하는데, 플루오린이 남아 다음 열처리 공정에서 다른 막에 표착이 돼 오류를 발생시킬 수 있다. 또 점점 각 층의 두께를 줄여가고 있어 텅스텐을 증착할 틈이 좁아 증착에 어려움을 겪을 수 있다.

램리서치가 제안한 방법은 막질에 남은 플루오린 농도를 최소화 하기 위해 프리커서를 바꾸는 것이다. 화학적기상증착(CVD) 때 플루오린 용량을 100분의 1 이하로 낮춘 저(Low) 플루오린 텅스텐 프리커서 또는 무(Free) 플루오린 텅스텐 프리커서를 개발했다.

프리커서를 바꿔도 텅스텐 막이 얇아지면 CVD 공정이 한계를 보일 수 있다. 이를 해결하고 더욱 얇은 박막 형성을 위한 원자층증착(ALD) 설비도 출시했다.

어플라이드머티리얼즈(AMAT), 도쿄일렉트론(TEL) 등 경쟁 업체들도 3D낸드의 각 필름 박막 두께를 줄이고 좀 더 선택비를 높일 수 있는 에칭 방식 등을 제안하고 있다.