애플 AP 전량 유치했던 비결인 인포(InFO) 이어... 또 한번의 게임체인저

전공정 기술 한계 해결하는 후공정... 파운드리-OSAT 간 경계 허물어

전공정만으로 반도체의 성능·전력소모량·면적(PPA)을 개선하던 시대는 끝났다. 전공정 제조만을 해온 반도체 외주생산(Foundry) 업계도 후공정 기술 확보에 나서면서 산업의 판도가 바뀌고 있다.

이를 주도하는 건 TSMC다. 올해 5나노 양산을 무사히 시작한 TSMC가 세 번째 반도체 후공정 기술 ‘SoIC(System on Integrated Chip)’의 상용화 막바지 작업에 돌입했다. 이르면 내년 SoIC가 적용된 5나노 반도체가 시장에 나온다.

3D 칩렛 기술 ‘SoIC’ 상용화 코앞

최근 반도체 설계자동화(EDA) 업체들은 TSMC의 차세대 후공정 기술 ‘SoIC’에 관련된 EDA 개발 도구(Tool) 출시를 앞두고 있다. SoIC는 TSMC가 지난 2018년 야심차게 선보인 후공정 기술로 관련 툴이 부족해 아직 상용화가 되지 못하고 있었다. 개발 툴이 나오게 되면 상용화는 시간 문제다.

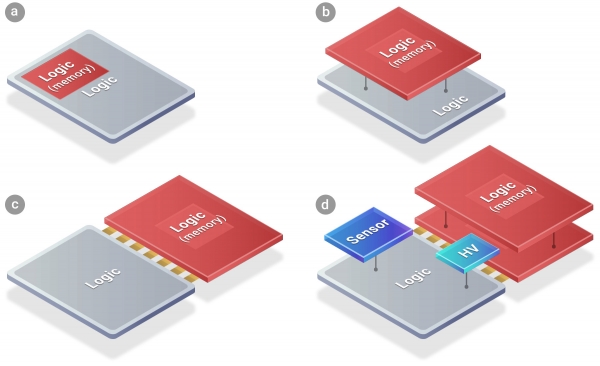

SoIC는 3D 칩렛(Chiplet) 기술이다. 기존 칩렛 기술이 시스템온칩(SoC)을 구성하는 여러 회로 블록을 서로 다른 공정에서 생산, 2D 평면으로 합쳤다면 SoIC는 각 회로 블록을 3D로 쌓는다. 수동·능동 소자까지 3D로 결합할 수 있어 솔루션 크기를 획기적으로 줄일 수 있고, 2D 평면으로 배치했을 때보다 칩 간 간격도 줄어 성능 및 대역폭을 개선할 수 있다.

기존 3D 적층 패키지 기술은 본딩 간격(bonding pitch)의 한계로 성능과 대역폭을 개선하기 어려웠다. 본딩은 웨이퍼와 웨이퍼, 혹은 칩과 웨이퍼를 전기적으로 연결하는 기술이다. 주로 공 모양의 범프(Bump)를 그 사이에 넣는 방식을 활용하는데, 범프 크기와 간격이 좁을수록 더 많은 범프를 넣을 수 있어 대역폭 및 성능을 개선할 수 있다.

하지만 플립칩(FC) 기술의 범프 간격은 백수십 마이크로미터(㎛)에 달한다. 실리콘관통전극(TSV) 기술과 FC 기술을 혼용하는 2.5D 패키지 기술조차 범프 간격이 50㎛ 언저리에서 좀처럼 내려가지 못하고 있다.

반면 SoIC는 범프 간격이 10㎛ 미만에 불과하다. 때문에 범프 밀도가 2.5D 패키지 기술보다 10배 높고, SoIC의 두 번째 버전인 SoIC+의 경우 범프 밀도가 2.5D 패키지의 1000배에 달한다. TSMC는 SoIC가 1㎟ 면적에 약 1만개의 상호 연결(Interconnection)을 구현할 수 있는 기술이라고 설명한다.

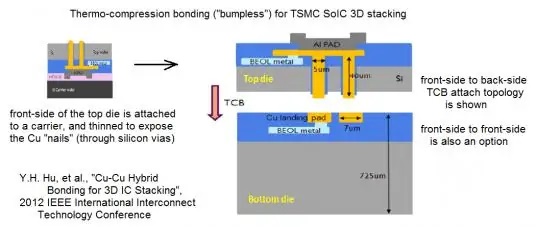

TSMC는 SoIC를 개발하기 위해 ‘범프 없는(Bump-less)’ 본딩 기술부터 연구했다. 기본 다이(die)에 얇은 구리(Cu) 패드를 형성하고, 위에 올라갈 다이나 웨이퍼에 TSV의 구멍(via)을 마치 손톱처럼 살짝 노출시켜 열 압착 본딩을 하는 방식이다. 전공정에서 진행해야하고 열 관리가 까다롭다는 단점이 있지만 기존 범프 기반 본딩 기술의 한계를 넘어설 수 있다.

후공정 업계 관계자는 “SoIC의 또다른 장점은 CoWoS(Chip-on-Wafer on Substrate)나 인포(InFo) 등 기존 TSMC의 후공정 기술과 함께 활용할 수 있다는 것”이라며 “상용화된다면 3D 패키지 역사의 큰 획을 긋는 기술이 될 것”이라고 말했다.

파운드리 업계는 왜 후공정 기술까지 손을 대기 시작했나

시장에서 후공정 기술의 중요성을 깨달은 건 지난 2016년 애플이 오랜 협력사였던 삼성을 제치고 TSMC를 애플리케이션프로세서(AP) 독점 생산 업체로 정했을 때다.

업계에서는 그보다도 3~4년 전부터 후공정 기술에 주목하기 시작했다. 20나노의 장벽을 넘을 기술로 ‘핀펫(FinFET)’이 개발됐지만 공정 개발 속도와 달리 성능 및 밀도 개선 속도는 점점 떨어지고 있었고, 연구개발(R&D)과 설비 투자에 드는 비용은 감당하기 어려운 수준으로 치솟았기 때문이다.

하지만 막상 파운드리 업체 중 후공정에 대한 투자를 늘린 업체는 찾아보기 어려웠다. 파운드리 업체가 패키지온패키지(PoP) 등 후공정 서비스를 제공하지 않은 건 아니었지만, 말 그대로 ‘서비스’ 개념이었기 때문이다.

여기에 전공정은 파운드리 업체가, 후공정은 외주반도체후공정테스트(OSAT) 업체가 외주를 받아 진행하는 게 일반적이라 자칫 OSAT 업체의 사업 영역을 침해한다는 인식을 줄 수 있었다. 파운드리 업체가 적극적으로 후공정을 개발할만한 상황이 아니었다는 얘기다.

그렇다고 OSAT 업체들이 기술 개발을 할만한 여력을 가지고 있었던 것도 아니었다. 3D 적층 기술인 TSV나 하이브리드 본딩 등은 대부분 전공정 장비로 진행된다. 전공정 생산 라인을 구축하려면 적어도 수천억원의 설비 투자가 진행돼야했다. 수백 마이크로미터를 다루던 업체들이 하루 아침에 수십 마이크로미터를 다루기도 어려웠다.

후공정 업체 A사 관계자는 “후공정 업계에서는 대당 50억원 짜리 장비도 비싼 편인데, 전공정 장비는 수백억원을 호가하는 것들이 많았다”며 “장비 업체와 협력해 기술 개발을 해야했지만 그럴만한 여유가 있는 업체는 손에 꼽았고 결국 개발만 하다 도중에 포기하거나 개발을 하더라도 양산은 하지 못한 업체들이 부지기수”라고 말했다.

그럼에도 TSMC는 2010년대 초반부터 패키지 기술에 공을 들이기 시작했다. 초기에는 고객들을 위한 서비스 개념으로 패키지 기술 개발을 다각화했지만, 전공정의 한계가 가시화되면서 후공정은 전공정과 함께 이 회사의 기술력이 됐다.

당시 선보인 CoWoS는 물론 애플의 선택을 받을 수 있었던 이유인 InFO 기술, 상용화를 앞둔 SoIC까지 전부 이때 연구개발이 시작됐다. 전공정 설비를 이미 가지고 있기 때문에 설비 투자 부담이 적었고, 개발에 수천억원을 쏟아부었지만 전공정과 후공정을 더해 얻은 시너지는 이를 뛰어넘었다.

뒤늦게 삼성전자 등 파운드리 업체와 OSAT 업체들이 고부가 반도체에 필요한 첨단 패키지 기술 개발을 시작했다. 삼성전자는 TSMC 패키지 기술의 대항마로 패널레벨패키지(PLP)를 내세웠지만 대량 양산 수준에 도달하기엔 아직 한계가 있다. 이 사실을 알고 있는 삼성전자 역시 투자를 머뭇거리고 있는 상황이다.(KIPOST 2019년 3월 13일자 <PLP, 패키지 기술의 미래가 되기 위한 3가지 난제> 참고)

전공정과 후공정, 사라지는 경계

업계는 갈수록 전공정과 후공정 간, 그리고 파운드리와 OSAT 업체간 경계가 사라질 것으로 내다본다. 첨단 패키지 기술이 발전할수록 양상은 더 확연해진다. 설계 단계에서부터 팹리스와 제조사가 협력해야하고, 전공정 설비들을 활용하는 기술이 많은만큼 OSAT 업체보다는 파운드리 업체에 유리한 게임이다.

파운드리 업체 입장에서도 후공정은 이제 단순 ‘서비스’가 아니다. 전공정에서 아무리 다이(die) 사이즈를 줄이고 입출력(I/O) 숫자를 늘렸다해도 후공정이 이를 뒷받침해주지 않으면 소용이 없다. 더군다나 반도체의 크기와 두께, 열 및 인터커넥트는 전공정보다 후공정과 더 밀접한 관련이 있다.

반도체 시장의 주축인 모바일과 서버 시장 또한 첨단 패키지 기술을 적용하지 않을 수 없는 상황이다.

애플이 AP를 더 얇게 만들기 위해 삼성 대신 TSMC를 채택한 것처럼 모바일 반도체 시장에선 칩의 폼팩터가 성능과 비견할 정도로 중요한 요인이다. 5세대 이동통신(5G)으로 스마트폰 한 대에 들어가는 무선 통신(RF) 부품 수가 증가하면서 시스템인패키지(SiP) 기술에 대한 수요도 커지고 있다.

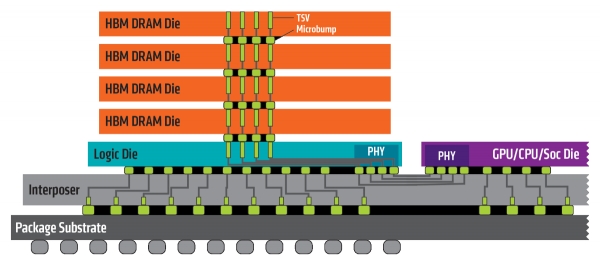

서버용 반도체 업체들도 첨단 패키지 기술의 주요 고객이다. 이들에게는 칩 간 거리를 줄여 전기적 신호의 이동 속도를 높이고 대역폭을 늘려 칩의 성능을 100% 활용하는 게 주된 이슈다. 고대역폭메모리(HBM)가 프로세서와 함께 2.5D 패키지로 묶여 서버 내로 들어간 것도 이 때문이다.

파운드리 업계 관계자는 “극자외선(EUV) 도입 이후 파운드리 업체가 두 곳밖에 남지 않은 것처럼 전공정 기술 발전 게임은 거의 막바지에 접어들었다”며 “이제는 전공정만이 아닌 후공정도 기술력의 척도로 작용할 것”이라고 말했다.