삼성전자, 14나노 핀펫 공정 ISP 내장한 이미지센서 상용화 개발 돌입

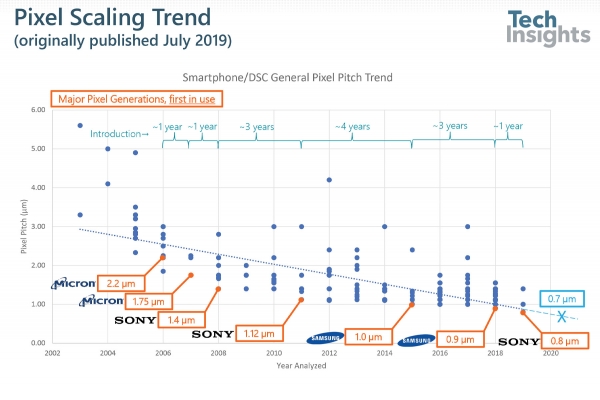

픽셀 크기도 0.7㎛로... TSV 및 하이브리드 본딩 등 연결 기술 발전도 빨라

상보성금속산화물반도체(CMOS) 이미지센서(CIS)는 센서 중에서도 가장 눈부신 발전을 해왔다. 10년 전 210만 화소, 고화질(HD)이 최대치였지만 최근에는 1억 화소가 넘는 이미지센서까지 나왔다.

이와 함께 발전해온 게 공정 기술이다. 최근에는 핀펫(FinFET) 기술까지 접목하려는 움직임이 보이고 있다.

핀펫까지 적용되는 이미지센서

업계에 따르면 최근 삼성전자는 14나노 핀펫 공정 기반 이미지센서 개발에 착수했다. 지난해 ‘국제반도체소자학회(IEDM) 2019’에서 파운드리 사업부가 관련 연구 결과를 발표한 데 이어 시스템LSI 사업부 CIS 설계 및 공정 기술팀과 협력해 상용화 개발에 나섰다.

이미지센서에서 ISP는 독립적으로 쓰이는 게 아니라 이미지센서에 종속돼 센서로부터 들어오는 데이터를 처리하는 역할을 한다. 현재 삼성전자의 이미지센서는 28나노 공정 기반 ISP를 쓰고, 소니 또한 28나노를 활용한다. 나머지 업체들이 대부분 40나노, 65나노 공정에 머무르고 있다는 점을 감안하면 기술 격차가 크다.

14나노 ISP가 필요한 이유는 잡음(Noise) 때문이다. 이미지센서 내 픽셀이 작아질수록 충분한 광량을 받을 수 없게 되고, 이는 다이나믹 레인지와 신호대잡음비(SNR)에 영향을 준다. 이 신호를 증폭시키고 잡음을 줄이려면 ISP의 공정이 업그레이드돼야 한다. 여기에 보통 스마트폰 한 대에 보통 3~4개의 카메라가 들어간다는 점을 감안하면 전력소모량도 줄여야 한다.

삼성전자는 지난해 발표한 연구 결과에서 14나노 ISP 기반 이미지센서의 플리커 노이즈 특성이 28나노 기반 이미지센서보다 약 64% 개선됐다고 설명했다. ISP 블럭의 전력 소모량도 28나노 대비 34%(12MP 기준)에서 최대 42%(144MP)까지 감소했다.

업계 관계자는 “올해 안으로 14나노 이미지센서 플랫폼을 상용화하는 게 목표지만 코로나19로 인해 수요 자체가 줄어들면서 아직 이를 장담할 수 없는 상황”이라며 “내부적으로는 개발은 계획대로 한다는 입장”이라고 말했다.

픽셀 스케일링, 0.8㎛의 장벽을 넘어라

CIS에서 로직 단인 ISP보다 중요한 건 픽셀이다. 지난해 0.8㎛까지 축소된 픽셀 크기는 올해 0.7㎛에 달할 것으로 보인다. 하지만 딥 트렌치 격리(DTI), 딥 다이오드용 임플란트 공정, 컬러 필터 및 마이크로렌즈의 광학 구조 축소 등 많은 과제가 남아있다.

업계가 처음으로 픽셀 크기의 장벽에 부딪힌 건 지난 2009년이다. 당시까지만 해도 이미지센서의 주류는 전면조사형(FSI)이었지만, 1.4㎛ 이하로 픽셀 크기를 줄이기가 어려웠다.

픽셀 크기를 줄이면 단위 픽셀이 받는 광량이 줄어들어 감도가 나빠지는데, FSI형 이미지센서는 빛이 렌즈와 컬러필터, 그리고 수 개의 메탈 층을 통과해야만 포토 다이오드에 도달했기 때문이다.

후면조사형(BSI) 이미지센서는 이 문제점을 해소하기 위해 등장했다. BSI형 이미지센서는 빛이 실리콘 기판 뒤에서 들어오기 때문에 포토 다이오드에 닿기까지 걸리는 시간이 짧아 감도가 FSI 대비 40% 정도 높다.

BSI 이미지센서를 채택한다 해도 무작정 픽셀 수를 늘릴 수는 없었다. 같은 면적에 더 많은 픽셀을 집어넣으려면 픽셀 자체의 크기도 작아야하지만, 픽셀과 픽셀 간의 거리(Pixel pitch)도 감소해야한다. 하지만 픽셀 피치가 지나치게 가까우면 누화(Crosstalk) 현상이 일어났다.

이에 픽셀과 픽셀 사이에 격벽을 세우는 DTI 기술이 개발됐다. DTI는 픽셀 사이에 두꺼운 실리콘 장벽을 세워 빛의 산란을 막는 기술로, 28나노 공정부터는 트렌치를 형성한 다음 고유전물(High-K) 막까지 증착해 간섭을 줄였다. 삼성전자는 전면 DTI(F-DTI) 기술을, 소니는 후면 DTI(B-DTI) 기술을 활용한다.

업계 관계자는 “픽셀 크기를 줄이려면 감도 손실을 막는 DTI 같은 기술들도 필연적으로 발전해야한다”며 “현재 삼성전자 내부에서는 이를 달성하기 위해 픽셀 내 트랜지스터 및 상호 연결 등 기본적인 설계 규칙들을 다시 손보고 있다”고 말했다.

실리콘관통전극(TSV)과 하이브리드 본딩, 둘 중 승자는

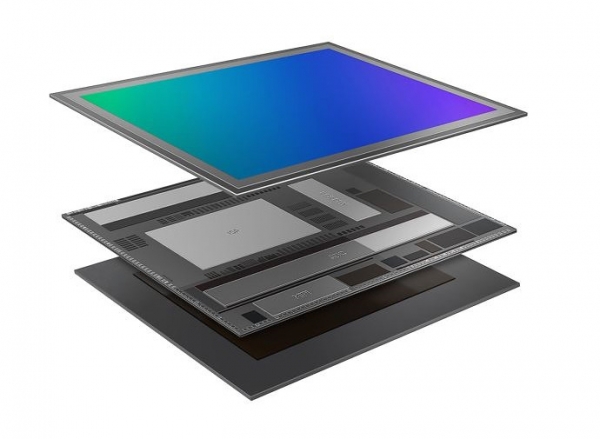

지난 2012년 소니가 픽셀 어레이 등 센서부와 ISP 등 처리부를 서로 다른 다이(die)에 만들어 쌓은 이미지센서를 내놓은 이후 적층형 이미지센서는 대세가 됐다.

지난 2018년, 소니와 삼성전자는 여기에 D램까지 합친 3중 이미지센서를 선보인다. 소니의 경우 센서부와 처리부(ISP) 사이에 임베디드 D램(eDRAM)을 끼워 넣어 데이터 처리 속도를 높였다.

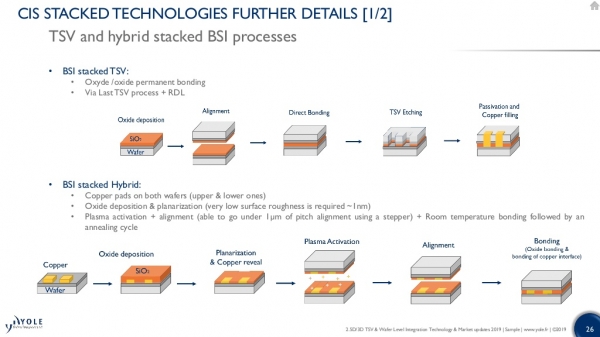

이미지센서의 적층 기술은 TSV와 하이브리드 본딩으로 나뉜다. 적층형 이미지센서의 붐이 막 불기 시작했을 때만 해도 TSV가 지배적이었지만 지난 2016년부터 소니가 TSV가 아닌 하이브리드 본딩을 채택하면서 파가 갈렸다. 삼성전자는 여전히 TSV 기술을 고집하고 있다.

TSV는 실리콘 기판에 구멍(via)을 뚫은 다음 구리(Cu) 같은 도전성 재료를 채워 다이와 다이를 수직으로 연결하는 기술이다. 보통 다이가 형성된 두 기판에 각각 실리콘옥사이드(SiO2) 층을 올린 다음 SiO2 면이 맞닿게 본딩한 후 TSV 식각, 구리 충진 등의 순서로 공정이 진행된다.

신뢰성 검사 등 계측검사(MI)가 까다롭고 공정 비용도 많이 들지만, 웨이퍼와 웨이퍼 사이의 인터커넥트 길이를 최소화할 수 있다는 장점이 있다.

하이브리드 본딩 기술은 Cu-Cu 상호 연결로 다이와 다이를 붙인다. 두 웨이퍼에 각각 구리 패드를 붙인 다음 SiO2 층을 깔고 산화시켜 구리 패드를 노출시킨 다음 플라즈마를 활성화해 두 웨이퍼의 각 구리 패드와 산화층을 다이렉트 본딩한다.

TSV보다 공정이 복잡하고 요구 특성이 높으나 기존 장비를 활용할 수 있어 비용이 저렴하다.

두 방법 모두 미세화에는 문제가 없지만, 차세대 이미지 센서 기술로 각광받는 ‘3D 하이브리드 BSI’ 기술로 나아가기에는 하이브리드 본딩 기술이 유리하다. 3D 하이브리드 BSI 기술은 픽셀 어레이를 제외한 나머지 로직 처리부, 아날로그 처리부 등을 모두 하이브리드 본딩으로 연결한다.

업계 관계자는 “3D 하이브리드 BSI 기술은 대규모 병렬 처리를 지원하기 때문에 센서의 모든 픽셀 데이터를 빠르게 읽고 쓸 수 있다”며 “삼성전자 또한 하이브리드 본딩 기술과 TSV를 모두 개발 중”이라고 말했다.