TSMC에 고객 몰리면서 낙수효과… 7나노까지 100% 가동률 보여

5나노부터는 또다시 기술 격차… TSMC 5나노 밀도 2배 가까이 개선

삼성전자 파운드리 사업부가 작년 하반기부터 100% 가동률을 보이고 있다. 아무리 급한 제품이라도 6개월을 대기해야할 정도다.

당장은 이 분위기가 이어질 것으로 보이지만, 5나노 공정 양산이 시작되면 또다시 삼성전자는 TSMC에 밀리게 된다. 7나노에서는 공정 사양이 비슷했지만 5나노에서는 차이가 크기 때문이다.

TSMC서 넘친 물량 삼성전자로...파운드리 낙수효과

반도체 업계에 따르면 최근 삼성전자는 협력사들에게 모든 공정에 대한 추가 프로젝트를 수주하지 않겠다고 밝혔다. 8인치 웨이퍼 생산라인부터 12인치 웨이퍼 생산라인까지 올해 생산 일정이 빠듯하기 때문이다. 특히 최첨단 공정은 기본 수개월 대기해야할 정도로 여유가 없다.

업계 관계자는 “아주 급한 프로젝트 아니면 생산이 밀리는 분위기”라며 “작년 가을 8나노 공정을 양산하려고 했는데 아직까지 생산 라인이 꽉 차 있다는 이유로 착수하지 못하고 있다”고 말했다.

삼성전자 파운드리 사업부의 가동률이 100%를 기록한 건 지난해 하반기부터다. 애플·자일링스·AMD·퀄컴 등의 고객사가 몰리면서 TSMC의 생산 능력(Capacity)이 꽉 찼고, TSMC에서 소화하지 못하는 물량이 삼성전자로 넘어왔다. AMD와 퀄컴, 엔비디아가 대표적이다.

하반기 애플의 물량이 급격하게 늘어나면서 TSMC의 공급 부족 현상은 더 심해졌다. 삼성전자도 공급 부족에 직면했다.

반도체 업계 관계자는 “삼성전자의 100% 가동률은 일종의 ‘낙수효과’”이라며 “IBM·테슬라를 제외한 대부분의 업체에게 삼성전자는 여전히 2차 공급사(Second Vendor)”라고 설명했다.

삼성전자가 TSMC의 2차 공급사가 될 수 있었던 까닭

완성품 업체가 부품 업체를 이원화하는 건 으레 있는 일이지만, 반도체 업계에선 드물다. 같은 공정이라도 사양이 다르면 완성품의 성능에 차이가 나기 때문이다. 특히 애플리케이션프로세서(AP) 같은 핵심 반도체는 완제품의 성능과도 밀접한 연관이 있다.

애플이 지난 2015년 AP ‘A9’ 생산을 삼성전자와 TSMC로 이원화했다가 두 제품의 성능 차이가 화제가 되면서 단일 공급사 체제로 바꾼 것도 이 때문이다. 퀄컴 또한 고사양 AP와 모뎀은 TSMC에게 맡기고 삼성전자에게는 저가형 모답(ModAP) 외주를 맡겨 모델별로 공급사를 이원화했다.

그럼에도 삼성전자가 TSMC의 2차 공급사가 될 수 있었던 건 TSMC와 7나노 공정 사양이 비슷했기 때문이다.

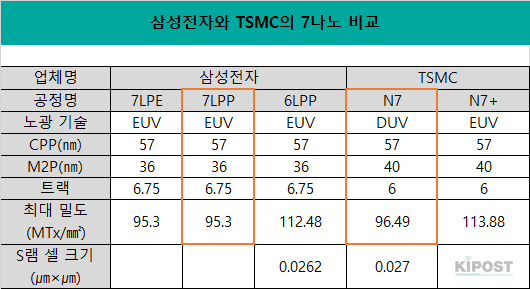

삼성전자의 2세대 7나노 공정(7LPP)과 TSMC의 1세대 7나노 공정(N7)의 사양은 서로 큰 차이가 없다. 삼성전자의 7LPP 공정이 1㎟ 면적에 9530만개의 트랜지스터를 만든다면, TSMC의 1세대 7나노 공정은 9649만개의 트랜지스터를 구현한다.

극자외선(EUV) 공정을 활용한 TSMC의 2세대 7나노 공정(N7+)은 밀도 사양을 높였지만, 삼성전자의 6LPP 공정과 비슷한 수준이다.

후공정 업계 관계자는 “14나노에서는 삼성전자와 TSMC의 기술 격차가 커 삼성전자가 파운드리 시장의 기술 주도권을 잡을 수 있었지만, 7나노에서는 TSMC가 앞섰다뿐 기술은 한끗 차이”라며 “삼성전자가 7나노에서 낙수효과를 볼 수 있었던 건 그 때문”이라고 말했다.

낙수효과에는 한계가 있다

하지만 낙수효과는 영원하지 않다. 상위 업체가 생산량을 늘리고 하위 업체와의 기술 격차를 벌리면 하위 업체로 떨어지는 물은 차츰 줄어들게 된다.

TSMC는 지난 2018년 150억달러(약 17조2785억원)에 이어 작년에도 140억달러(16조1266억원) 규모의 설비투자를 단행했다.

작년 초만 해도 100억달러(11조5190억원)를 투자할 계획이었지만 수요가 증가하면서 규모를 키웠다. 회사는 작년 10월 올해 투자 계획도 상향 조정해 올해 또한 전년과 비슷한 정도로 생산능력 확대에 투자할 계획이라 밝혔다.

반면 삼성전자의 파운드리 투자는 화성 극자외선(EUV) 라인을 제외하고 수년째 보완 및 증설 투자로 진행됐다. TSMC와 생산능력 차이가 6배 이상 나는 까닭에 내부에서 여러 번 신규 투자 논의가 진행됐지만 갖은 이유로 투자까지 이어지지 못했다.

업계 관계자는 “타사보다 공정이 다양하지 않고, 첨단 공정은 쓸 수 있는 업체가 한정돼있어 좀처럼 투자를 하지 못하는 것”이라며 “파운드리 업황이 전방 시장과 직결돼있다는 것도 위험 요인 중 하나”라고 말했다.

평택 반도체 2공장에 들어서는 4개 생산 라인 중 1개 라인이 파운드리 용도로 배정됐다지만, 그마저도 메모리 업황에 따라 뒤집어질 공산이 크다.

물론 기술 격차를 좁히면 생산량을 늘리지 않아도 낙수효과는 이어진다. 아무리 TSMC라도 첨단 공정의 수요를 모두 충족할만큼 막대한 투자를 하기는 어렵다.

성능 밀리는 5나노부터는 수주 안갯속

문제는 7나노 다음 첨단 공정인 5나노에서 삼성전자와 TSMC의 기술 격차가 또다시 벌어진다는 점이다.

양산 시점만 놓고 보면 두 회사의 차이가 크지 않다. TSMC는 애플의 차세대 AP ‘A14 바이오닉(가칭)’, 삼성전자는 ‘갤럭시노트 11(가칭)’에 들어갈 AP 생산 시점에 맞춰 5나노를 대량 양산 체제로 전환할 계획이다. 애플의 아이폰과 삼성전자의 갤럭시노트는 늘 비슷한 시기에 출시된다.

하지만 성능은 TSMC가 우세하다. 7나노 공정 개발에 사활을 걸었던 삼성전자와 달리 TSMC는 5나노 공정에 방점을 찍었다. 16나노(삼성은 14나노)와 28나노 공정이 전력소모량 대비 성능이나 가격 대비 성능의 이점으로 주류 공정이 된 것처럼, 5나노 또한 그렇게 될 것이라는 판단에서다.

TSMC는 지난달 개최된 ‘국제반도체소자학회(IEDM) 2019’에서 5나노 공정의 세부 사양과 공정 개발 진척도를 공개했다.

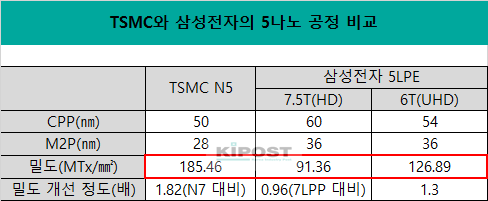

TSMC의 5나노 공정은 7나노 공정보다 밀도를 최대 1.84배(로직 기준) 높였다. S램 밀도는 1.3배 개선했다. 실리콘게르마늄(SiGe) 기반 고이동도채널(HMC)를 도입해 7나노 공정 대비 속도는 15% 빨라졌으며, 전력소모량은 30% 줄였다.

TSMC의 5나노 공정에서는 10개 미만의 EUV 층이 30개 미만의 기존 액침 불화아르곤(ArFi) 레이어를 대체하게 된다. 7나노에서는 컨택트(Contact) 형성에 필요한 3~4개의 층을 EUV로 만들었다. EUV 층은 늘었지만, 전체 마스크 숫자는 줄어든다.

장비 업계 관계자는 “더 많은 EUV를 쓰기엔 아직 장비 처리량(throughput)이 좋지 않다”며 “7나노와 마찬가지로 마스크 숫자를 줄이되 최대한 처리량을 유지하는 방향으로 EUV를 적용한 것”이라고 말했다.

삼성전자의 5나노(5LPE) 및 4나노(4LPE) 공정은 7나노 공정의 확장판이다. 때문에 5나노 공정은 7LPP와 설계자산(IP)의 상당부분을 공유한다. 설계 측면에서 공정 전환(migration)은 쉽지만 그만큼 성능 개선 정도가 크지 않다는 것을 의미하기도 한다.

삼성전자는 5나노 공정이 7나노 공정 대비 면적을 25% 줄였고 전력 효율은 20%, 속도는 10% 개선했다고 밝혔다.

회사가 난해 ‘Arm 테크콘(techcon) 2019’에서 공개한 바에 따르면 5나노 공정에는 두 개의 선택지가 있다. 7.5T 고밀도(HD) 라이브러리와 셀의 높이를 낮춰 면적·전력소모량을 개선한 6T 초고밀도(UHD) 라이브러리다.

하지만 UHD 라이브러리조차 밀도가 126MTx/㎟로 TSMC 5나노(185.46MTx/㎟)보다 한참 낮고, 전력효율과 면적 및 속도 모두 TSMC의 개선 정도에 못 미친다.

업계 관계자는 “삼성 내부적으로는 5나노까지 TSMC에 뒤쳐지는 게 어쩔 수 없다고 판단하고 있다”며 “트랜지스터 구조가 핀펫(FinFET)에서 게이트올어라운드(GAA)로 바뀌는 3나노 때 다시 승기를 잡겠다지만, 과연 가능할지 의구심이 든다”고 말했다.