인텔과 달리 코어와 메모리, 입출력(I/O) 성능 두루 개선

TSMC 및 글로벌파운드리와 협력해 칩렛 구조 혁신 이뤄

지난해까지 서버 중앙처리장치(CPU) 시장의 범접할 수 없는 1위는 여전히 인텔이었다. 2017년 AMD가 ‘에픽(EPYC)’ 프로세서로 시장에 재진입했지만 인텔의 점유율은 끄떡도 하지 않았다.

올해는 다르다. AMD는 2세대 에픽 프로세서(코드명 로마) 출시 발표와 함께 이미 이 제품을 구글·트위터가 채택했다고 밝혔다. 서버 제조사도 AMD의 CPU로 제품군을 늘릴 계획이라고 설명했다. 전과는 다른 자신감을 내비친 셈이다.

인텔도 긴장하고 있다. 지금까지 이 시장을 이끌어온 인텔 입장에서는 점유율을 5%만 잃어도 타격이 크다. AMD의 목표는 내년까지 10%의 점유율을 달성하는 것이다.

램 페디보틀라(Ram Peddibhotla) AMD 데이터센터 제품 수석 부사장에게 AMD의 2세대 에픽 프로세서가 이전과 달리 큰 호응을 받고 있는 비결을 물었다.

AMD의 2세대 에픽 프로세서, 데이터센터의 새로운 표준

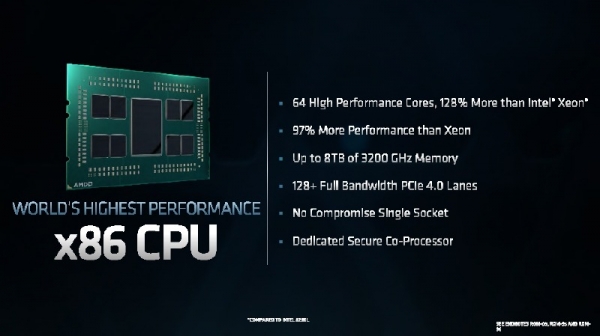

먼저 AMD 2세대 에픽 프로세서는 전작과 비교할 수 없을 정도로 높은 성능 개선을 이뤄냈다. 경쟁사인 인텔의 최상위급 서버 프로세서보다 성능이 97% 높고, 1세대 에픽 프로세서보다 부동소수점(FP) 성능도 2배 뛰어나다. x86 아키텍처를 가진 서버용 프로세서 중에선 최초로 7나노 공정을 써 전력소모량 당 성능도 높다.

인텔이 서버 CPU의 컴퓨팅 성능을 강화하고 메모리와 I/O의 균형을 맞추는 전략을 택했다면, AMD는 모듈식 설계로 가격 경쟁력을 확보하고 가상서버(VM) 등 현재 데이터센터 업계의 수요에 맞춰 I/O와 메모리 성능을 높이는 전략을 세웠다.

램 수석 부사장은 이 제품을 한 마디로 “데이터센터의 새로운 표준”이라고 정의했다. 출시 이후 온갖 벤치마크 사이트에서 이 제품은 수십개의 세계 기록을 달성했다.

그는 “2세대 에픽 프로세서는 성능, 아키텍처, 보안 측면에서 혁신적인 기능을 제공한다”며 “코어는 물론 입출력(I/O), 메모리까지 선도적인 성능을 기록했고, 이 성능이 바로 고객들이 가장 원하는 것”이라고 설명했다.

데이터센터 업계가 성능을 고집하는 이유는 간단하다. 비용이다. 프로세서 두 개가 하던 일을 프로세서 한 개로 처리할 수 있다면, 굳이 서버 랙을 두 개나 설치할 필요가 없다. 단순히 프로세서 하나를 아끼는 게 아니라, 전체 서버 투자 비용을 줄일 수 있다는 얘기다.

램 수석 부사장은 “경쟁사의 최상위급 제품보다 성능이 2배 높기 때문에 AMD의 2세대 에픽 프로세서를 채택하면 총소유비용(TCO)을 절반으로 줄일 수 있다”며 “돈과 인력을 덜 들이고 더 많은 일을 수행할 수 있는 셈”이라고 말했다.

성능 개선의 비밀 - ① 아키텍처

사실 AMD의 1세대 에픽 프로세서(코드명 나폴리)는 데이터베이스(DB)를 다루는 데이터센터에 적합하지 않다는 평가가 많았다. AMD조차 아키텍처에 한계가 있다는 것을 감안, 데이터베이스에는 그다지 초점을 맞추지 않았다.

2세대 에픽 프로세서는 데이터센터에서 다루는 다양한 워크로드를 모두 지원한다. AMD는 이를 위해 마이크로 아키텍처부터 코어, I/O, 메모리를 모두 갈아치웠다.

AMD의 2세대 젠(Zen2) 아키텍처는 전작에 쓰인 1세대 젠(Zen1) 아키텍처를 계승한다.

먼저 젠2 아키텍처는 다음 실행될 조건문이 어떤 곳으로 분기할 것인지를 확실히 알게 되기 전에 미리 추측하는 기술인 분기 예측 성능을 개선했다. 이를 통해 코어의 정수 처리량을 늘렸고, 부동소수점 처리 성능(연산 파이프)을 2배 향상시킬 수 있었다.

여기에 데이터 경로도 줄었고 벡터 레지스터 파일도 2배 커져 메모리에서 데이터를 받아올 때 걸리는 유효 대기 시간을 단축했다. 다시 말해 데이터를 더 빨리 불러와서, 더 빨리 처리한다는 얘기다.

램 수석 부사장은 “이를 통해 2세대 젠 아키텍처의 사이클 당 명령어 처리 횟수(IPC) 성능은 평균 15%, 서버별 작업 부하에서는 최대 23% 증가했다”며 “코어 레벨에서 엄청난 성능 향상이 있었다”고 설명했다.

성능 개선의 비밀 - ② 칩렛

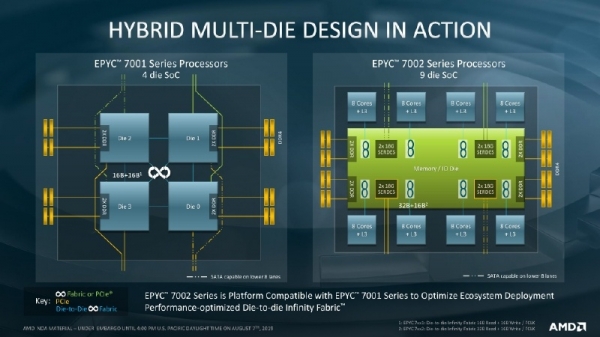

단순히 코어와 공정만으로 이 제품이 이토록 높은 성능 향상을 이뤄낼 수 있었던 건 아니다. AMD는 1세대 에픽 프로세서부터 칩렛(Chiplet) 기술을 활용했다. AMD에서는 이를 ‘하이브리드 멀티 다이 접근법(Hybrid multi die approach)’의 일환이라고 설명한다.

칩렛은 서로 다른 공정에서 생산된 서로 다른 종류의 반도체를 하나의 기판 위에 놓고 연결, 패키지하는 기술이다.

지금처럼 첨단 공정에서 시스템온칩(SoC)의 모든 다이(die)를 일괄적으로 만들면 단가도 올라가고 첨단 공정 도입으로 인한 위험 부담도 크다. 칩렛을 적용하면 성능 좋은 반도체를 보다 저렴한 가격에 팔 수 있게 된다.

2세대 에픽 프로세서에서 AMD는 7나노 공정을 활용함과 동시에 칩렛 구조를 강화했다.

1세대 에픽 프로세서는 연산(Logic)과 메모리, I/O가 하나에 담긴 네 개의 SoC로 구성됐다. 각 SoC 다이는 인피니티 아키텍처로 연결됐다. 2세대는I/O와 메모리를 일일이 분리해 하나로 모으고, 연산 다이는 8개를 넣었다.

I/O와 메모리 다이는 글로벌파운드리의 14나노 공정에서, 로직은 TSMC의 7나노 공정에서 생산된다. 램 수석 부사장은 양사와 수년간 협업을 통해 이 구조를 개발, 적용했다고 설명했다.

각 SoC에 있는 I/O를 빼면서 연산 코어들은 더 많은 작업을 할 수 있게 됐다. 코어 수 자체를 늘리는 것도 충분히 가능했고, AMD는 여기에 캐시 메모리를 넣어 메모리 접근성을 강화했다. 메모리는 가장 최신 기술인 DDR4 3200㎒까지 지원하며, I/O 대역폭은 512GB/s다.

그는 “연산 반도체는 첨단 공정을 쓰는데 문제가 없지만, I/O는 공정 기술의 발전을 상대적으로 따라잡지 못한다”며 “이미 성숙한 공정인 14나노에서 I/O를 만들었고, CPU 연산 단은 최첨단 공정인 7나노 공정을 써서 성능과 안정성을 동시에 확보했다”고 말했다.

성능 개선의 비밀 - ③ 인피니티 패브릭

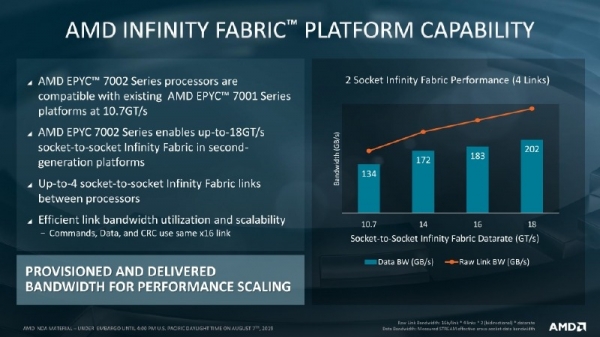

하지만 칩렛 구조를 도입하면서 문제가 하나 생겼다. 다이와 다이 사이를 데이터가 수없이 오가야하는데, 이 때 걸리는 지연시간이 길어졌고 대역폭 또한 좀처럼 늘리기 어려웠다.

한계를 극복하기 위해 AMD가 도입한 게 인피니티 패브릭(Infinity fabric)이다. AMD는 다이와 다이 사이, 소켓과 소켓 사이의 모든 연결을 인피니티 패브릭으로 통일했다.

2세대 에픽 프로세서에 적용된 2세대 인피니티 패브릭 기술은 대역폭과 전송 속도 개선을 목표로 개발됐다. 전력 소모량은 1세대와 다르지 않다.

다이와 다이 사이의 대역폭은 클럭 당 32바이트(단방향) 기술과 16바이트 기술을 동시에 적용해 필요한 곳에서 1세대(16바이트) 대비 2배 이상 많은 데이터가 움직일 수 있게 했다.

지연시간도 줄였다. 1세대 나폴리는 SoC 다이가 다른 SoC 다이 내 메모리에 접근할 때 141나노초(ns)의 지연시간이 걸린다. 2세대 로마는 메모리가 중앙에 있는 다이(die)에 모두 결합돼있어 연산 다이가 메모리에 접근할 때 걸리는 지연시간이 104나노초 밖에 걸리지 않는다.

내장된 I/O가 PCIe 4.0 표준을 따른다는 것도 강점이다. 인텔 등 경쟁사들은 아직 PCIe 3.0 표준을 따르고 있다. PCIe 4.0은 전송 대역폭이 PCIe 3.0보다 2배 넓다. AMD의 2세대 에픽은 차세대 2소켓 메인보드에서 1세대 대비 1.3배 많은 168개의 PCIe 4.0 인터페이스를 지원한다.

램 수석 부사장은 “2세대 에픽 프로세서는 우리가 기술 리더십을 가지고 있다는 것을 증명하는 계기가 됐다”며 “젠3 아키텍처가 적용된 3세대 에픽 프로세서(코드명 밀라노)도 설계가 끝났다”고 말했다.