삼성전자 PLP보다 약간 더 큰 규격

장비 업계와 협업해 파일럿 라인 확장

인텔이 패널레벨패키지(PLP)를 준비하고 있다. 다양한 공정에서 생산된 여러 반도체 다이(die)를 한 번에 후공정(Packaging)하는 게 목표다.

이를 위해 차세대 반도체 인터커넥트 기술도 개발한다. 반도체 다이(die)를 서로 더 가깝게 붙이거나 적층해 두 칩간의 대역폭을 넓히는 데 초점을 뒀다.

인텔, PLP 연구 본격화… 목표는 이기종 통합 시스템인패키지(SiP)

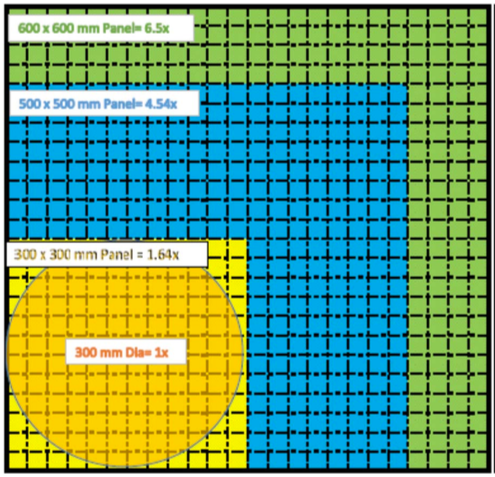

업계에 따르면 최근 인텔은 PLP에 활용할 패널 크기를 정하고 이를 장비 협력사들에게 통보했다. PLP 자체와 함께 PLP를 자사의 인터커넥트 기술과 접목하는 것을 연구개발(R&D)할 계획이다.

한 장비 업계 관계자는 “협력사들과 장비를 공동 개발, 파일럿 라인의 생산량을 늘릴 계획으로 알고 있다”며 “인텔의 PLP용 패널은 삼성전자의 PLP 패널(500㎜×415㎜)보다 약간 크다”고 말했다.

11일 세미콘웨스트(SEMICON WEST 2019) 부대 행사 ‘테크토크(TechTALK)’에서 라둘 마네팔리(Rahul Manepalli) 인텔 수석 연구원도 “미래 고성능컴퓨팅(HPC)에는 이기종 통합 시스템인패키지(SiP)가 적합하다”며 “PLP의 성능을 더 개선할 수 있다면 SiP 대신 PLP를 쓰는 게 가격 측면에서 낫다”고 설명했다.

SiP는 후공정을 끝낸 여러 종류의 반도체를 하나의 기판 위에 올려놓고 패키징하는 기술이다. PLP는 패널 그 자체가 기판 역할을 한다. 패널 위에 여러 반도체 다이(die)를 올려놓고 한 번만 패키징하면 마더보드 하나가 뚝딱 생긴다. 별도 기판이 사라지기 때문에 패키지 두께를 줄이고 성능은 개선할 수 있다.

웨이퍼레벨패키지(WLP)나 칩스케일패키지(CSP)로 했을 때보다 처리량(Throughput)도 많아 비용·시간 측면에서도 유리하다.

하지만 PLP 기술은 아직 애플리케이션프로세서(AP)·중앙처리장치(CPU)처럼 입출력(I/O) 숫자가 많은 반도체를 패키징할 정도로 발전하지 많았다.

고성능 반도체를 패키징하려면 미세화 수준(L/S)이 적어도 2㎛ 이하는 돼야한다. 하지만 업계는 아직 10㎛도 달성하지 못했다.

이를 구현하려면 새로운 장비 개발이 불가피하다. 수백 마이크로 단위에 익숙한 PCB 장비 업체들도, 패널처럼 큰 기판을 다뤄본 적이 없는 후공정 장비 업계도 어려울 수밖에 없다. 인텔이 장비 업계와 공동 개발을 추진하는 것도 이 때문이다.

라둘 마네팔리 수석 연구원은 “PLP가 이기종 패키지에 쓰이려면 1㎜ 당 250개 이상의 I/O 단자를 형성할 수 있을 정도의 성능을 확보하고, 반도체 전공정에서 쓰는 장비와 계측 방법, 자동화, 제어 기술 등도 적용할 수 있어야 한다”고 말했다.

더 가깝게 배치하고, 위·아래로 쌓고… 인텔의 인터커넥트 기술

마네팔리 수석 연구원은 이날 행사에서 전날 인텔이 발표한 차세대 패키징 및 인터커넥트 기술 코이밉(Co-EMIB), ODI(Omni-Directional Interconnect), 엠디오(MDIO) 등도 상세히 설명했다.

고성능컴퓨팅(HPC) 시장을 겨냥, 모두 반도체 다이(die)들이 서로 보다 빠르게, 더 많은 정보를 주고받을 수 있게 한 게 특징이다. 현재는 웨이퍼 레벨 수준이지만, PLP에 적용될 가능성을 배제할 수 없다.

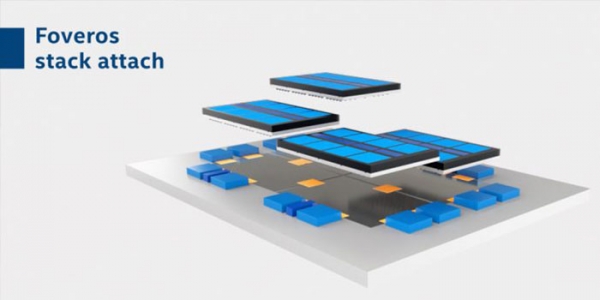

‘Co-EMIB’은 ‘임베디드 멀티-다이 인터커넥트 브릿지(EMIB)’ 기술과 ‘포베로스(Foveros)’를 합친 개념이다.

‘포베로스’는 인텔이 지난해 공개한 3D 적층 기술로 베이스 다이가 형성된 웨이퍼 위에 칩렛 다이가 만들어져있는 웨이퍼를 올려 본딩(Bonding)하는 게 핵심이다. 베이스 다이와 칩렛 다이는 서로 다른 공정에서 생산되며, 내년 출시될 노트북PC 프로세서 ‘레이크필드(Lakefield)’에 적용된다.

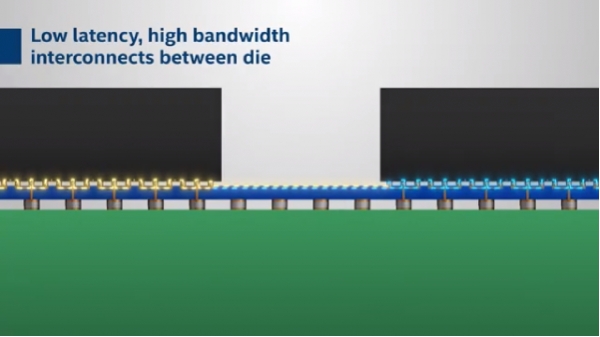

EMIB은 칩과 칩 사이를 수평으로 연결하는 인터커넥트 기술이다. 현재 인텔을 제외한 나머지 업체들은 2.5D 반도체를 만들 때 값비싼 인터포저에 재배선층(RDL)을 만들어 서로 다른 칩을 연결하지만, EMIB은 패키지 기판 내부에 형성되기 때문에 상대적으로 가격이 저렴하다.

이 둘을 합친 게 ‘Co-EMIB’이다. CPU·GPU 같은 로직(Logic) 반도체는 서로 쌓아버리고, 고대역폭메모리(HBM)는 EMIB으로 연결하겠다는 것이다. 이 기술은 미국 에너지부에 납품할 오로라 슈퍼 컴퓨터에 처음 적용될 전망이다.

‘Co-EMIB’가 칩 간을 연결하는 기술이라면, ODI는 칩 내부에 층층이 쌓여있는 각 레이어에 전력이 잘 전달될 수 있도록 하는 수직 통로다. 유기 기판에 칩렛 다이를 올려놓고 실리콘관통전극(TSV)보다 큰 구멍을 뚫는데, 이게 바로 ODI다.

두께가 두꺼워 저항과 지연시간은 낮추고 대역폭은 높일 수 있다. 기존 파워딜리버리네트워크(PDN)를 발전시킨 기술이다. TSV 숫자도 줄일 수 있어 수율 확보도 보다 쉬워진다.

MDIO는 첨단 인터페이스 버스(AIB)를 개선한 3D 적층용 물리 인터페이스다. 인텔은 MDIO가 AIB보다 핀 속도, 대역폭 밀도가 2배 이상 높으면서도 전력소모량은 AIB와 비슷한 수준이라고 밝혔다.