고유전율 소재 필수… 구조도 바뀐다

D램 회로 선폭이 10나노 중반대에 접어들었다.

업계는 당장 내년 1z 나노부터 극자외선(EUV) 노광 기술을 적용하는 방안을 검토 중이다. 생각보다 기술 난이도가 높아서다. 하지만 EUV를 도입한다고 해서 끝나는 게 아니다. EUV로도 해결하지 못하는 난제들이 산적해있다.

커패시터 유전막, 두 마리 토끼를 잡아라

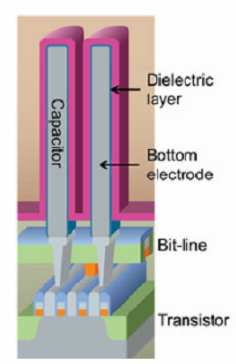

D램 셀이 동작하려면 셀의 크기와 집적도에 관계 없이 특정 값 이상의 정전용량(C)을 가져야한다. 정전용량(C)은 커패시터의 유효 표면적(A)과 커패시터를 감싸고 있는 유전막의 유전율(ε)에 비례하고, 유전막의 두께(L)에 반비례한다.

D램 미세화가 진행될수록 커패시터는 점점 가늘어지고 표면적도 줄어든다. 동작 특성조차 확보하기 어렵다는 얘기다. 1x나노 D램을 기준으로 300㎜ 웨이퍼 1장에는 셀 13조개가 빼곡히 들어차있다. 커패시터의 종횡비(A/R)는 8년 전 25(30나노 대)에서 60(1x나노)까지 늘어났다.

그동안 업계는 커패시터를 둘러싸고 있는 유전막의 두께를 줄이면서 이에 대응해왔다. 삼성전자는 10나노대에 진입하면서 원자층증착(ALD)을 활용, 유전막 두께를 옹스트롬(Å, 10분의 1나노) 단위로 줄였다.

하지만 소재를 바꾸지 않고 두께를 줄였다가는 유전막이 제 역할을 하지 못해 셀 간 간섭 현상이 발생하거나 전하가 너무 빠르게 새어나가는 문제가 발생한다. 즉, 고유전율 소재로 유전막 재료를 교체해야 한다.

업계가 1x나노 D램의 유전체로 쓰고 있는 소재는 지르코늄옥사이드(ZrO2)로 두께는 약 7Å다. 1z 나노대까지는 지르코늄옥사이드 2개 층 사이에 고유전율 소재를 넣는 MIM(Metal-insulator-Metal) 구조로도 가능하지만 그 이후부터는 유전막 두께를 6Å 이하로 줄여야해 또다시 소재를 바꿔야 한다.

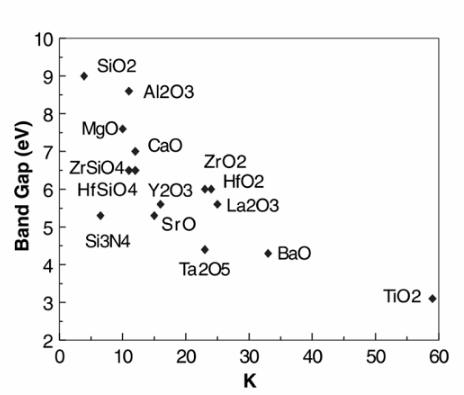

고유전율 소재가 없는 것은 아니다. 하지만 보통 유전율이 높은 소재는 에너지밴드갭이 적다. 에너지밴드갭이 적으면 누설 전류에 취약하다. 유전율과 에너지밴드갭 값을 모두 만족하는 소재를 찾기가 쉽지 않다.

차기 소재로 유력한 것은 티타늄(Ti) 계열이다. 티타늄옥사이드(TiO2)는 밴드갭 값이 3.5고, 유전상수(K) 값은 60에 가깝다. 티타늄(Ti)의 밴드갭 값은 95, 유전상수는 5.5다.

이와 별개로 학계에서는 유전체 입자의 크기를 줄이거나 불순물을 첨가하는 등 결정 구조를 제어하는 방안을 연구하고 있다. 하지만 불순물이 산화루테늄(RuO2), 이리듐(Ir), 백금(Pt) 등 희소금속이라 가격 상승의 요인이 된다.

업계 관계자는 “정전용량 값이 20~25fF에서 10fF로 줄어들면서 동작 특성 문제가 심화됐다”며 “커패시터 내부를 구성하는 전극(Electrode) 소재를 바꾸는 방안도 검토되고 있지만 유전막보다 더 중요한 역할을 하기 때문에 바꾸기가 쉽지 않다”고 설명했다.

하이케이메탈게이트(HKMG), 이번엔 D램이다

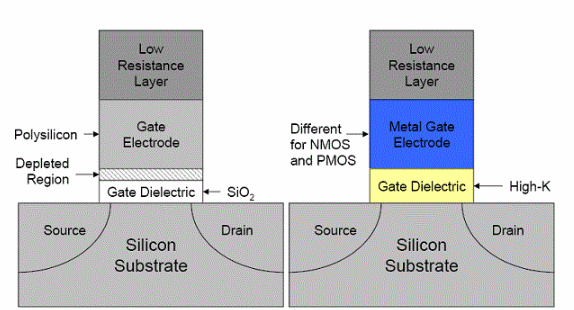

D램 고집적화의 두 번째 문제는 스위치 역할을 하는 게이트 아래 있는 절연층의 두께다. 보통 이 절연층은 고온으로 실리콘을 산화시켜 실리콘옥사이드(SiO2)를 형성해 만든다.

게이트 절연층이 두꺼울수록 트랜지스터를 작동시키기 위한 문턱전압 값이 높아지고, 반대로 절연층이 얇아지면 문턱전압 값이 낮아져 전력소모량이 줄어드는 효과가 발생한다. 하지만 두께를 지나치게 줄이면 누설 전류 문제가 발생하게 된다.

2x나노부터 1y나노까지 D램 게이트 산화막의 두께는 6Å에서 좀처럼 내려오지 못하고 있다. 한계에 부딪혔다는 얘기다.

이에 업계는 1z나노 D램이나 그 이후부터 로직(Logic) 반도체 공정에서 썼던 하이케이메탈게이트(HKMG)를 적용할 계획이다.

HKMG는 게이트 산화막 두께를 극도로 줄이거나 없애는 대신 고유전율 소재를 올리고 게이트(폴리실리콘)를 메탈로 바꾸는 기술이다. 게이트 산화막과 폴리실리콘 사이 공핍층(Depletion layer)을 없앨 수 있고, 전체 두께를 줄이면서도 누설 전류를 방지할 수 있다. 전류에 대한 감도도 높아진다.

다만 얇은 막을 더 많이 쌓아야해 결함을 제어하기 어려워지고, 재료와 공정이 추가되는만큼 제조단가가 비싸진다. EUV 공정까지 적용된다는 점을 감안하면 판매단가 상승은 불가피한 셈이다.

업계 관계자는 “D램 가격이 많이 올랐다지만 기술 난이도에 비하면 아직도 싼 편”이라며 “EUV와 HKMG까지 적용되기 때문에 단가를 올리지 않으면 수익성을 확보하기 어렵다”고 설명했다.

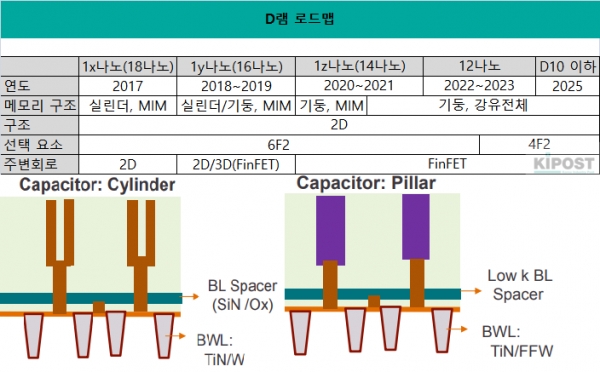

10나노 이하 D램, 원통형(Cylinder)에서 기둥(Pillar)으로

기술 발전이 벽에 부딪히면서 로직 반도체는 2차원(2D)에서 3차원(3D) 핀펫(FinFET) 구조로, 낸드플래시는 2D에서 3D 수직 적층 형태로 모양을 바꿨었다.

D램도 마찬가지다. 10나노 이하부터는 커패시터의 형태가 U자 실린더 모양에서 기둥 모양으로 바뀐다.

현재 D램은 전극(Electrode)이 U자로 휘어있고 이를 유전층이 둘러싸고 있는 구조다. 미세화할수록 U자 아래에 깔리는 유전막의 두께가 윗부분보다 두꺼워져 거꾸로된 원추 모양이 되고, 커패시터의 정전용량을 확보하기 어려워진다.

이에 업계는 커패시터를 기둥 형태로 바꾸고, 누설전류를 막기 위해 주변을 두꺼운 고유전율 유전체로 둘러싸는 방안을 연구하고 있다.

종횡비가 60 이상인 셀 사이 사이를 균일하게 파내려면 식각 장비의 선택비(Selectivity)가 높아져야하고, 그 사이에 유전층을 고르게 입히려면 ALD 장비를 활용해야한다.

특히 ALD는 세미 배치 타입 기준으로 시간당 웨이퍼 처리량이 플라즈마 화학기상증착(PE-CVD)의 수십분의 1에 불과하다. 소재와 두께에 따라 달라지지만, 지금 상태로는 1시간에 웨이퍼 2장만 겨우 처리하는 수준에 불과하다.

ALD 장비 구조를 1번에 1장의 웨이퍼만 처리하는 싱글 타입, 수장의 웨이퍼를 돌려가며 증착하는 세미 배치 타입, 웨이퍼를 여러 장 둔 상태에서 공정을 진행하는 배치 타입 등으로 바꿀 수 있지만 배치 타입으로 갈수록 처리량은 늘어나지만 균일성 등이 떨어진다는 단점이 있다.

이에 장비 업계에서는 새로운 프리커서의 개발이 불가피하다고 설명한다. 흡착과 화학 반응을 번갈아 하는 방식이라 장비 단에서 처리 속도를 높이기는 힘들다는 지적이다.

장비 업계 관계자는 “반응에 필요한 에너지가 적고 고압에도 안전한 프리커서가 개발돼야한다”며 “구조까지 바뀌어야 하는 만큼 제조사와 장비·소재 업체가 서로 협력할 수 밖에 없는 상황”이라고 설명했다.